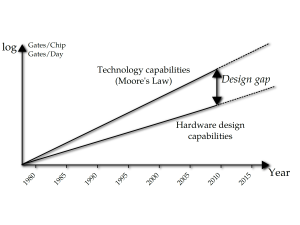

Přeloženo jako mezera (nedostatek) v možnostech návrhu, Design Gap je již jednou objevil při návrhu čipů objevila okolo roku 2000 a byl diskutován na konferenci 40. Design Automation Cconference, v souvislosti s uvedením 90 nm technologie. Bylo možné (s dodržením Moorova zákona) vyrobit vyšší počet tranzistorů na čipu, ale v návrhu pro ně nebylo mnoho využití. Řešením tehdy bylo větší využití opakování IP (design reuse) až do používání celých platforem, což vedlo k implementování čipů SoC s mnoha miliony tranzistorů.

Na letošním, 55. DAC, programový manažer Andreas Olofsson v DARPA (Defense Advanced Research Projects Agency ) pro mikrosystémy, poznamenal, že tato mezera opět vzniká. Tentokráte je způsobená cenou návrhu, když se cena návrhu čtverečního milimetru vymyká kontrole. DARPA vytvořila několik projektů, kterými chce na nově vznikající nedostatky reagovat.

Podle odborníků je čas na další větší změnu v EDA prostředí pro návrh čipů, jakou bylo řešení předchozí mezery. Současné nedostatky jsou možná způsobeny nepředvídatelným chováním při malé změně vstupních parametrů. (Zvýšení frekvence o 2 dekády vede k nárůstu plochy o 6%.)

Řešení vznikající mezery by mohlo spočívat ve využití umělé inteligence (deep learning a data mining), která by nabízela efektivnější modely, které se přizpůsobí realitě rychleji. Toho právě chce DARPA docílit spoluprací více společností a shromážděním využitelných modelů pro AI.

Více o tomto tématu se můžete dočíst v článcích: Remember the design gap? It’s back, DARPA Plans a Major Remake of U.S. Electronics, EDA learns to love AI nebo na stránkách Design Automation Conference.

(radek)@cadware.cz