V této části seriálu o procesorových modulech SQM4 představíme zatím posledního, nejnovějšího zástupce této řady – modul SQM4-ZY7. Základ tohoto modulu tvoří dvoujádrový procesor ARM® Cortex™-A9 kombinovaný na jednom čipu s periferiemi a hlavně s výkonným hradlovým polem. Tento unikátní kombinovaný systém byl vyvinut firmou Xilinx a je známý pod souhrnným označením Xilinx® All Programmable SoC – rodina Zynq®-7000. Modul SQM4-ZY7 na sobě integruje obvod Zynq Z-7020 s potřebnými napájecími zdroji, s 1G pamětí DDR3L, sériovou 16MB pamětí Flash, až dvěma gigabitovými Ethernet PHY, USB kontrolérem a dalšími periferními obvody.

Pro svůj kompaktní design 43 × 43 mm a možnost SMD montáže přímo na základní aplikační desku představuje modul SQM4-ZY7 (obr. 1) ideální řešení pro levný a rychlý vývoj aplikací, které potřebují vysoký výpočetní výkon a hradlové pole, ale které samy o sobě nevyžadují návrh celého plošného spoje ve vysoké třídě přesnosti a v mnoha vrstvách.

V tomto čísle časopisu DPS představíme kromě platformy Zynq také vývojové nástroje Xilinx pro návrh logiky hradlového pole a pro vývoj software pro procesory ARM CortexA9. Předmětem příštích dílů bude vývoj jednoduché aplikace, která demonstruje možnosti platformy Zynq, modulu SQM4-ZY7 a základní desky EasyBoard určené pro prototypový vývoj se všemi moduly typu SQM4. Na konci našeho seriálu bychom tedy měli mít pro SQM4-ZY7 hotovou funkční aplikaci, která komunikuje s uživatelem pomocí UART konzole, umožňuje síťový přístup z internetového prohlížeče protokolem HTTP, a navíc implementuje řadič displeje v hradlovém poli. Pro jednoduchost se s naší pokusnou aplikací nebudeme pouštět do oblasti aplikace operačního systému Linux, který je pro takto výkonné procesorové platformy běžný. Naše aplikace bude jednoúčelová a zcela bez použití operačního systému. Pro demonstraci technologie a principů vývoje to bude jistě dostatečné, a snad i srozumitelnější – zejména pro velkou skupinou českých vývojářů zabývajících se vývojem softwaru pro běžné mikrokontroléry – např. pro mikrokontroléry firmy Freescale, pro něž jsme představili moduly SQM4 v minulých číslech DPS.

Platforma Xilinx Zynq spojuje v jediném čipu dva světy, které spolu sice úzce souvisejí, ale přesto se poměrně zásadně liší v přístupu k řešení zadaných úloh. Svět „klasického programování“ v jazycích, jako je C, C++, se zde potkává se světem návrhu polovodičových součástek v jazycích VHDL, Verilog, SystemC apod. Možnosti, které toto spojení přináší, jsou skutečně nevídané a existuje celá řada úloh, které by jinak ani řešit nebylo možné, např. vysokorychlostní zpracování signálů. Aplikace, které kombinují procesor s hradlovým polem, jsou samozřejmě běžné, ale mít obě části v jediném čipu umožňuje propojit je způsobem a rychlostmi, které by s dvoučipovými řešeními nebyly dosažitelné. Klíčový je zde samozřejmě fakt, že obě části systému mají vysokorychlostní přímý přístup do systémové paměti a ke sdíleným periferiím.

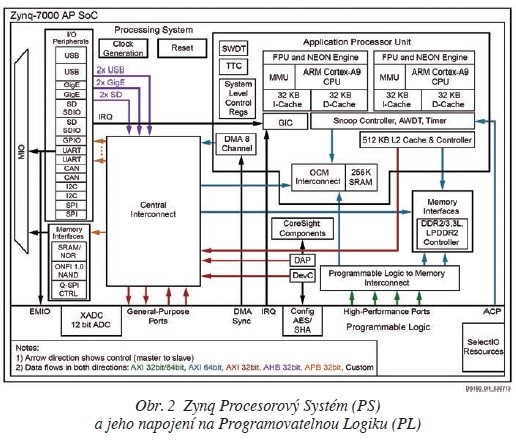

Pojďme si oba světy v krátkosti přiblížit: procesorový subsystém (PS) platformy Zynq (obr. 2) je víceméně klasickou implementací architektury ARMv7-A. U všech zástupců celé rodiny Zynq je PS založeno na dvou identických procesorových jádrech CortexA9, každé s vlastní 32kB instrukční a datovou pamětí cache, s FPU a NEON jednotkami pro urychlení výpočtů v plovoucí desetinné čárce a v multimediálních aplikacích. Každé jádro je také vybaveno standardní jednotkou MMU pro ochranu a virtualizaci fyzické paměti, která je nezbytná pro běh vyšších operačních systémů, jako je např. Linux. Procesorový systém pak dále tvoří sdílená kombinovaná paměť cache 512 kB, statická paměť 256 kB pro obecné využití, řadič externí paměti DDR, řadič přerušení GIC, řadič DMA a několik periferních modulů, včetně dvou gigabitových Ethernet MAC, USB 2.0, řadiče NAND, SD-CARD, QSPI, timeru TTC a dalších. Samozřejmostí jsou komunikační moduly UART, SPI, I2C, CAN a GPIO, a také jednoduchý 12-bitový ADC převodník, který může být kromě jednoho externího vstupu využit také na diagnostiku vlastních napájecích napětí a operační teploty systému.

Pokud se na PS Zynqu podíváme kritičtěji a porovnáme jej s konkurenčními mikroprocesorovými systémy, může se nám zdát vybavení platformy Zynq „chudé“. Chybí například jednotka pro zpracování či generování audio a video signálů, rozhraní pro HDMI displej a podobně. Také počet portů standardních komunikačních periferií není nijak závratný, na většině zástupců rodiny Zynq najdeme například jen dva UART a SPI porty. Tento nedostatek je však jen zdánlivý. Součástí PS je totiž také několik vysokorychlostních portů sběrnice AXI a přerušovacích signálů IRQ, které v obou směrech propojují procesorová jádra s velmi výkonnou programovatelnou logikou (PL). Periferie, které uživatel pro danou aplikaci potřebuje, si může sestavit (tzv. syntetizovat) na míru s funkčností, kterou potřebuje. Jednoduchých periferií typu UART by bylo možné i do nejmenšího člena rodiny Zynq syntetizovat opravdu stovky – pokud by to aplikace vyžadovala. PL je však typicky určena pro syntézu složitějších obvodů, jako je například zpracování videa, rozpoznávání obrazu, syntéza hlasu apod.

Klíčem k úspěchu platformy Zynq je použití standardního sběrnicového systému AXI3 a AXI4, který byl definován firmou ARM a slouží k propojení „master“ řídicí části systému (CPU, DMA, Ethernet apod.) se „slave“ periferní částí systému (typicky paměť, periferní registry apod.). Standard AXI je podporován na hardwarové úrovni přímo procesorovým systémem. Na straně programovatelné logiky je pak uživateli k dispozici opravdu bohatá nabídka knihovních prvků, které jsou s AXI kompatibilní a pomocí nichž je tvorba a syntéza vlastních periferií velmi jednoduchá. Navíc pro systémy zpracovaní nebo generování signálů je v knihovně také mnoho prvků podporujících i standard AXI4-Stream, který je rovněž definován firmou ARM. AXI4- -Stream sjednocuje přístup k datovým proudům organizovaných v paketech nebo i přímo jako nekonečné posloupnosti hodnot. Knihovní prvky zahrnují směrovače, řadiče priorit, koncentrátory, filtry a paměti FIFO, které jsou všechny díky standardu vzájemně kompatibilní a jednoduše propojitelné. S využitím těchto prvků je možné signál velmi snadno předzpracovat a nasměrovat programovatelnou logikou ze svého zdroje až do paměti procesorového systému nebo obráceně.

Periferní obvody, které si pro PL můžete sami navrhnout, mohou implementovat vámi definovanou sadu řídicích registrů, mohou komunikovat s vnějším světem přes vstupně-výstupní piny a mohou mít i přímý přístup do paměti systému nebo i k dalším periferiím. Jak už jsme naznačili úvodem, v jednom z příštích dílů našeho seriálu si v rámci vývoje ukázkové aplikace nadefinujeme jednoduchý řadič displeje, který dokáže promítnout vzor ve tvaru šachovnice ve zvolené barvě. Zdrojový kód periferie v jazyce Verilog, jakož i zdrojový C kód celé aplikace, včetně HTTP serveru, je už dnes dostupný všem uživatelům modulů SQM4-ZY7 na stránkách www.sqm4.com.

Na závěr tohoto stručného výčtu technologií, které jsou v systému Zynq k dispozici bude dobré shrnout si literaturu, která je pro správné pochopení všech principů nutná. Sada volně dostupných vývojových nástrojů firmy Xilinx obsahuje aplikaci nazvanou Documentation Navigator (DocNav), která velmi usnadňuje práci a přístup k technické dokumentaci celého portfolia výrobků Xilinx. DocNav hlídá aktuálnost všech dokumentů, nabízí stažení posledních verzí apod. Z nabídky DocNav pro začínající uživatele platformy Zynq doporučujeme:

Po registraci na stránkách firmy Xilinx získáte možnost stáhnout si zdarma vývojové nástroje pro vybrané (menší) zástupce všech rodin obvodů programovatelné logiky i obvodů Zynq. Modul SQM4- -ZY7, který si v tomto článku představujeme, je založen na obvodu XCZ7020, který je nástroji s volně dostupnou licencí podporován. Firma Xilinx už několik let dodržuje režim, ve kterém vydává 4 verze nástrojů během roku a označuje je stylem rok-tečka-verze. V době práce na tomto textu je aktuální verze 2015.2, příklady k SQM4-ZY7 jsou nyní dostupné pro verzi 2014.4. Nové verze nástrojů jsou až na drobnosti zpětně kompatibilní, a „většinou“ přinášejí vylepšení a opravy chyb. Slovo „většinou“ je zde namístě, neboť jsme od 2013.2, kdy jsme na SQM4-ZY7 začali pracovat, poznali i verze, které byly méně stabilní a hůře použitelné. Z vlastní zkušenosti tedy doporučujeme raději konzervativní přístup k novým verzím a nástroje aktualizovat jen v případě, že nová verze přináší vylepšení nutné pro pokračování ve vývoji aplikace. Každopádně je dobrá praxe novou verzi nástrojů vždy otestovat a projektové soubory vytvořené ve starších verzích zálohovat pro případ, že by bylo nutné se k nim vracet.

Jednotlivých nástrojů, které jsou během vývoje pro Zynq potřeba, je celá řada. Dají se však rozdělit do dvou hlavních skupin: Vivado a SDK. Nástroje v balíku Vivado slouží pro návrh, syntézu a testování programovatelné logiky. Jedná se o poměrně nové integrované prostředí, plně skriptovatelné v jazyce TCL, které nahrazuje předchozí generace nástrojů ISE, XPS, WebPack, Chipscope a jiné. Nástroj SDK je integrované prostředí pro vývoj software v C a C++ s kompilátorem GCC a související sadou utilit. SDK je založeno na populární platformě Eclipse/CDT, rozšířené o funkce specifické pro práci s procesorovými jádry Zynq a Microblaze od firmy Xilinx. Sami jsme otestovali, že jak Vivado, tak i SDK je možné provozovat na systémech s Microsoft Windows, i na vybraných distribucích Linuxu.

Nástroje Vivado a SDK jsou na sobě nezávislé, ale pro úspěšné založení projektu v SDK je nutné mít k dispozici definiční soubory vygenerované v nástroji Vivado. Ve Vivadu totiž vývojář definuje konfiguraci celého systému Zynq, přiřazení IO pinů, frekvence hodin, nastavení DDR apod. Tuto konfiguraci pak SDK použije pro vygenerování inicializačního kódu nutného k nastartování systému po resetu nebo během ladění.

Pro snadné založení projektu ve Vivadu je k dispozici několik předdefinovaných konfigurací pro vývojové desky dodávané přímo firmou Xilinx nebo jejími partnery. Značné popularitě se těší i komunitní projekt ZedBoard, který je zde rovněž přímo podporován. Uživatelé modulů SQM4 mají na stránkách www.sqm4.com k dispozici sadu souborů, které po nakopírování na správné místo v instalační složce rozšíří podporu i na všechny dostupné verze SQM4-ZY7. S takto upravenou instalací je pak založení nového projektu velmi jednoduché. Projekt je automaticky nastaven na správný typ DDR3L pamětí, hodinových signálů a přiřazení vstupně výstupních pinů k periferiím v PS.

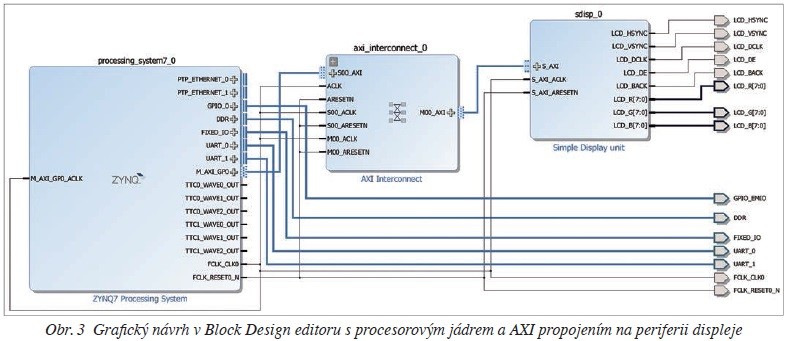

Typicky prvním krokem po založení nového projektu je specifikace souboru, který definuje ostatní piny použité v aplikaci a založení tzv. top-level modulu v jazyce Verilog nebo VHDL. Top-level modul reprezentuje celý systém a sdružuje v sobě všechny části PL i PS. Vstupní a výstupní signály tohoto modulu jsou pak již přímo mapované na konkrétní piny pouzdra zvoleného obvodu. Pro snadnější napojení syntetizovaných periferií s procesorovými jádry a zbytkem PS je možné použít i grafický návrhový systém, tzv. Block Diagram Designer (BD) – na obr. 3. V BD je procesorový systém PS reprezentován jako jeden blok, ke kterému je možné snadno připojit periferní obvody – ať už z knihovny, nebo vytvořené vlastními silami a zapouzdřené do grafických objektů. V jazycích VHDL i Verilog je velmi běžné používání konfigurovatelných parametrů, které se dají uživatelem nastavit, a ovlivnit tak chování dané periferie nebo modulu. Během návrhu v BD je možné periferním obvodům takové parametry zadávat pohodlně přímo z grafického rozhraní. U knihovních prvků Xilinx, které jsou většinou extrémně konfigurovatelné, je grafická konfigurace značně praktičtější než vkládání hodnot parametrů do zdrojového kódu. Také propojování signálů sběrnic AXI je ve zdrojové podobě zdlouhavá a nudná práce, kterou použití BD velmi ulehčuje.

V našem ukázkovém projektu použijeme BD pro pohodlné nastavení a propojení PS s naší syntetizovanou periferií řadiče displeje pomocí sběrnice AXI4- -Lite. Ve zdrojové podobě pak budeme definovat jen top-level modul a samozřejmě i vlastní logiku řadiče displeje. Nástroj SDK poté použijeme k vytvoření softwarového projektu, který se v případě práce se Zynq vždy skládá minimálně ze tří částí: tzv. hw-platform, což je inicializační kód vygenerovaný na základě nastavení čipu, dále z knihovny BSP s drivery pro periferie PS a z vlastního kódu aplikace.

V příštím dílu seriálu shrneme rozdíly mezi dvěma nejběžněji používanými jazyky pro definici programovatelné logiky a vybereme jeden z nich pro vývoj naší ukázkové aplikace s modulem SQM4- -ZY7.