Technologie LoRa, šifrování na způsob ECC (Elliptic Curve Cryptography), agregace signálu, strojové učení nebo ještě efektivnější práce s grafikou – to vše slibují nové referenční návrhy společnosti Lattice Semiconductor určené pro programovatelná hradlová pole FPGA iCE40 UltraPlus™.

Své uplatnění najdou v chytrých telefonech, nositelné elektronice, dronech, kamerách s 360° záběrem, rozhraních HMI, průmyslové automatizaci a také při zvyšování bezpečnosti internetu věcí. Zde všude mohou ve spojitosti se senzory a opakovanými výpočty, které jejich činnost provázejí, těžit právě z účinného paralelního zpracování a odlehčit přitom výkonově náročnějším aplikačním procesorům. Bateriově napájeným aplikacím totiž nová hradlová pole přináší osm bloků signálového procesoru nebo též 1,1 Mb paměti typu SRAM (na stránkách DPS jsme nejmenší FPGA s rozšířenou pamětí a osmi DSP krátce zmiňovali již v únoru). Ale zpět k referenčním návrhům představeným výrobcem na sklonku června v této celé zprávě.

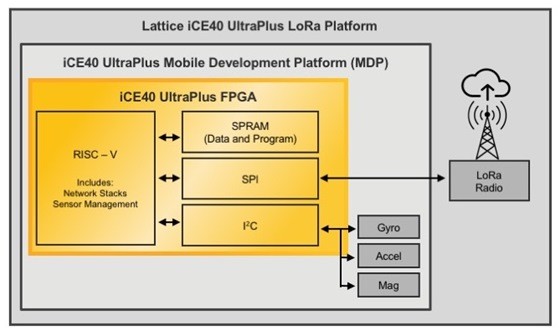

Možnosti strojového učení, resp. umělé inteligence staví na algoritmech pro trvale aktivní a přesto nízkopříkonovou detekci obličeje na základě výstupu z obrazového senzoru. S grafikou budou dále např. souviset trvale přítomná zobrazení času na displeji nositelného zařízení v režimu nízké spotřeby, zatímco bude jeho aplikační procesor uspán. Se šifrováním dat z čidel před jejich odesláním do Cloudu zase pomůže „ECC Security“ a chybět nesmí ani již zmiňované řízení vf části kompatibilní s technologií LoRa – viz blokový diagram.

Další informace naleznete přímo na stránkách Lattice Semiconductor.

(robenek) @dps-az.cz