Optimalizace návrhu FPGA s ohledem na návrh DPS

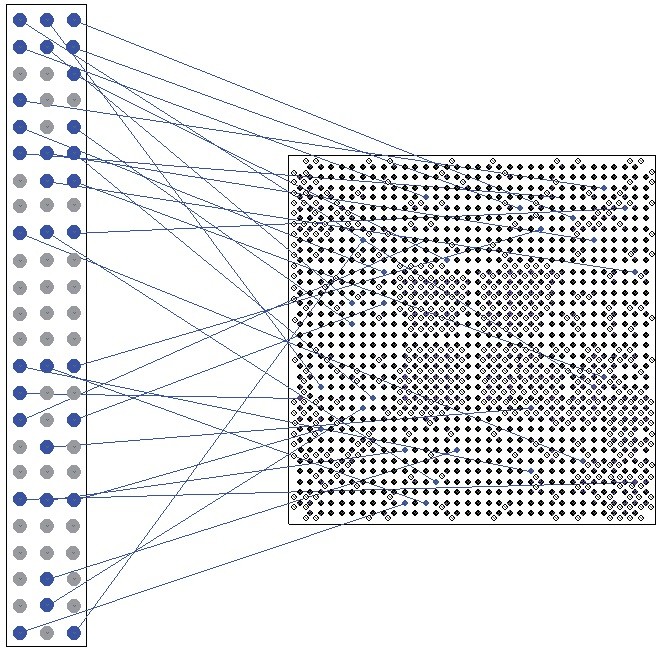

Návrh FPGA a návrh DPS jsou dvě rozdílné činnosti, které snad pouze výjimečně zvládá jeden návrhář. V dnešní době, kdy mají FPGA více než 1 000 vývodů, může jejich výsledný návrh pěkně zamotat hlavu návrháři desky. Problémem bývá nevhodné přiřazení I/O vývodů pouzdru FPGA součástky, kdy již položení plošných spojů od FPGA může být velmi obtížné, nemluvě o dodržení požadavků kladených na spoje, např. předepsané délky (obr. 1). Dodatečná úprava přiřazení fyzických vývodů FPGA představuje přinejmenším podstatné časové zdržení celého procesu návrhu FPGA i DPS.

Obr. 1 Nevhodné přiřazení vývodů FPGA

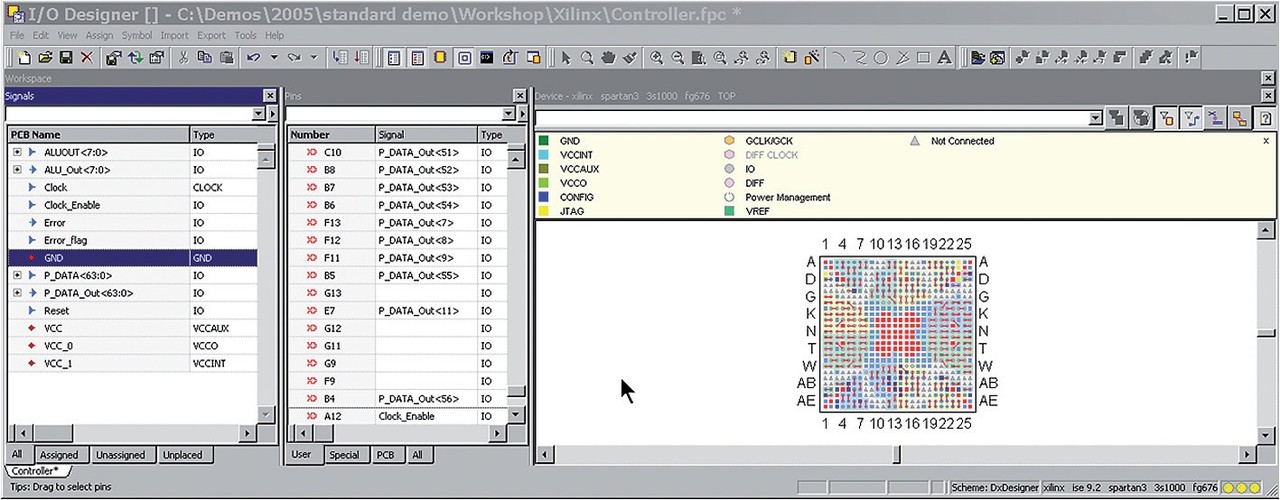

Program I/O Designer firmy Mentor Graphics [1] je určen pro optimální řešení vhodného přiřazení fyzických vývodů FPGA s ohledem na umístění součástky na dané desce. Je prostředníkem mezi HDL nástroji pro návrh FPGA a návrhovým systémem DPS. I/O Designer je nástrojem pro data management mezi HDL popisem FPGA a pouzdrem součástky na desce (obr. 2). Optimalizuje návrh jak jednotlivých FPGA, tak i jejich skupin.

Obr. 2 Proces přiřazení I/O vývodů FPGA pouzdru součástky

I/O Designer spolupracuje s programem pro kreslení schémat DxDesigner (Mentor Graphics), kde se automatizuje proces generování potřebných symbolů pro schéma i desku. Plně přitom podporuje respektování pravidel dodavatelů FPGA pro správné přiřazení I/O na daném pouzdru součástky. Eliminuje dodatečné změny v návrhu kvůli chybám v synchronizaci FPGA-DPS. Přiřazení fyzických vývodů FPGA na pouzdru součástky se provádí s ohledem na konkrétní umístění FPGA na desce a v návaznosti FPGA na připojené součástky.

Mezi mnohé výhody práce s I/O Designer patří:

- Významné zkrácení doby nutné pro návrh FPGA a DPS

- Eliminace dodatečných změn na DPS způsobené chybami v interface FPGADPS

- Zjednodušení návrhu DPS, spoje od FPGA jsou kratší a směřují přímo k cíli

- Zvýšení spolehlivosti desek a snížení nákladů na jejich výrobu.

Výrobce programu uvádí, že I/O Designer redukuje dobu potřebnou pro návrh FPGA a DPS zhruba o 1 týden na každých 500 vývodů FPGA zapojených na desce.

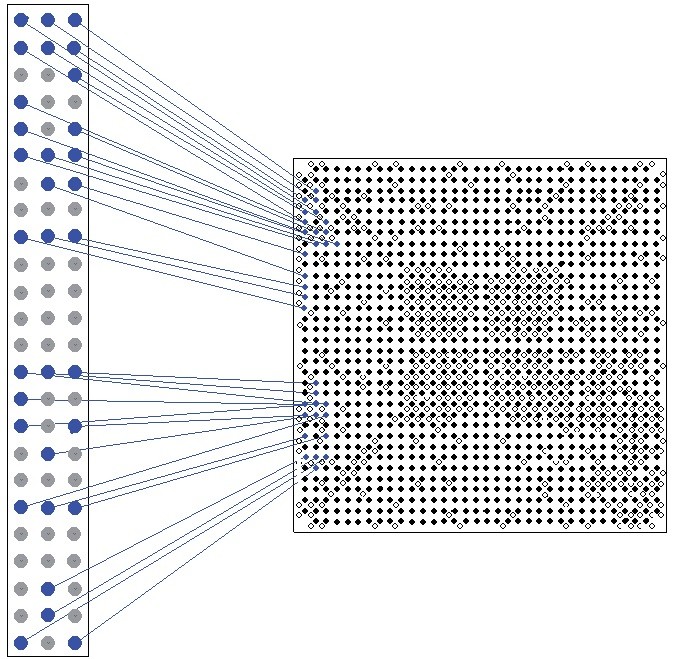

I/O Designer podporuje návrh FPGA od firem Actel, Altera, Lattice a Xilinx a navazuje na programy pro návrh FPGA jak od firmy Mentor Graphics (FPGA Advantage), tak i od výrobců FPGA. Výsledkem práce v I/O Designer je FPGA součástka optimalizovaná pro konkrétní použití na dané desce plošných spojů (obr. 3).

Obr. 3 FPGA optimalizovaná pro danou desku

Na webové stránce [1] je ke stažení článek „A Fundamentally Different Approach to FPGA I/O Design“ popisující použití programu I/O Designer při návrhu desky ve firmě Agilent. Tato deska měla 11 součástek FPGA typu Virtex 4 LX po 1 148 vývodech, které byly mezi sebou provázány sběrnicí 10 GBPS. FPGA součástky měly zadány velmi komplexní pravidla a různá omezení. 28vrstvá deska obsahovala přibližně 9 800 součástek a 9 500 spojů. Firma Agilent ušetřila zhruba 5 měsíců při návrhu FPGA a desky plošných spojů a proto se rozhodla používat I/O Designer při návrzích FPGA na všech svých pracovištích.