Proč provádět Signal Integrity analýzy už ve schématu

I když se tzv. Signal Integrity analýza zabývá přenosem signálu plošným spojem, nemusí se provádět jenom na navržené desce, ale už i ve stadiu návrhu zapojení čili ve schématu. Většinou nedělá problém si představit, jak poměry na navržené desce mohou ovlivnit kvalitu přenosu digitálního signálu plošnými spoji, ale jak tomu je při kreslení elektrického zapojení? Vždyť ani neznáme rozmístění součástek, délky plošných spojů, na které vrstvě budou spoje tažené atd. A proč se vůbec zabývat přenosem signálu plošným spojem ještě před návrhem desky?

Zkusme nejdříve zodpovědět druhou otázku, a to proč se zabývat problematikou Signal Integrity už ve schématu. Tento zdánlivě nelogický postup má však docela logické vysvětlení – pokud se Signal Integrity analýza provede až na navržené desce a ukáže se, že vše není zcela v pořádku, potom se nalezené problémy těžko odstraňují, aniž by se musela navržená deska upravovat. Problémy se budou nejspíše týkat délek některých plošných spojů a to znamená buď změnu rozmístění součástek na desce, nebo vložení sériových odporů či jiných zakončovacích členů na daný spoj. Někdy to také může znamenat přeložit některý plošný spoj dovnitř desky nebo ho zcela přemístit, zejména když jsou problémem přeslechy. V každém případě to vždy znamená zásah do již navržené desky, což přináší přinejmenším nemalé časové zdržení a opětovnou kontrolu upravené desky.

Z tohoto důvodu je lepší provést základní analýzu zaměřenou na kvalitu přenosu signálu už před vlastním návrhem desky. I když nejsou ještě všechny informace o desce známy, lze mnohé z nich předpokládat a podle toho celou analýzu provést. Výsledkem jsou potom doporučení pro návrh desky, která zohledňují podmínky, při kterých se analýza prováděla a které je potřeba v návrhu desky akceptovat. Takto navržená deska bude s největší pravděpodobností vyhovovat i při konečné analýze navržené desky. Změnit dodatečně hodnotu sériového odporu nebo jiných zakončovacích členů ještě ve schématu je jistě mnohem jednodušší, než hledat volné místo pro jejich umístění na desce nebo měnit rozmístění součástek.

Podívejme se tedy stručně na analýzu přenosu signálu ve stadiu kreslení schematického zapojení. Použijeme k tomu program Hyperlynx LineSim firmy Mentor Graphics, která nabízí také obdobný program pro analýzu již navržené desky (Hyperlynx Board-Sim).

Úvodem je třeba se zmínit o jednom mýtu, který předpokládá nutnost provedení analýzy celého zapojení. Taková analýza však není nutná, protože možné problémy přenosu signálu se rozhodně netýkají celého elektrického zapojení, ale jenom jeho některých částí. Jedná se o části elektrických obvodů, které spínají velmi rychle, a je lhostejné, jestli se tak děje jen občas nebo pravidelně s nějakou frekvencí. Jakmile se stav signálu mění velmi rychle, řekněme řádově v několika nanosekundách a rychleji, potom se plošný spoje chová jako přenosová linka, na které dochází ke zpoždění signálu, odrazům, zakmitávání, vyzařování atd. Na rozdíl od analýzy již navržené desky, která se provádí automaticky na celé desce, ve schématu se analyzují pouze ty části zapojení, které si určí sám vývojář.

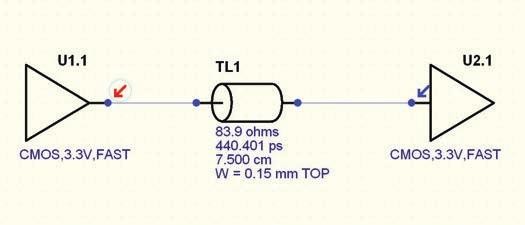

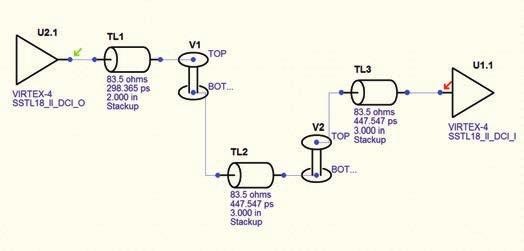

Obr. 1 Zapojení pro analýzu přenosu signálu plošným spojem

Zapojení, které se analyzuje (obr. 1), je vytvořeno ve vlastním editoru programu LineSim, takže je nezávislé na konkrétním typu programu pro kreslení schémat a návrh desek plošných spojů. Výstup rychle spínající součástky (vlevo) je připojen přes plošný spoj (symbol v podobě válečku) na vstup napojené součástky (vpravo). Toto je typický způsob kreslení zapojení za účelem Signal Integrity analýz. Symbolům výstupu i vstupu se přiřadí z knihovny programu modely konkrétních součástek, nebo alespoň modely jejich skupiny součástek, které mají podobné parametry (zde např. CMOS 3,3V Fast). Symbolu plošného spoje se zadají parametry, které u daného spoje na desce předpokládáme (šířka a délka spoje, strana desky). Zde je nutné podotknout, že ještě předtím se musí zadat základní informace o složení vrstev desky (layer stackup), jejich tloušťkách a materiálu. S výjimkou délky plošného spoje, která je odhadnuta, jsou ostatní parametry známé. V našem ukázkovém případu byla délka plošného spoje odhadnuta na maximálně 75 mm. Program okamžitě spočítá impedanci takového spoje (bere se v úvahu i umístění spoje na určité vrstvě desky) a zpoždění signálu.

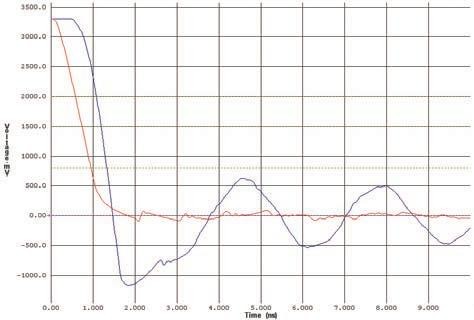

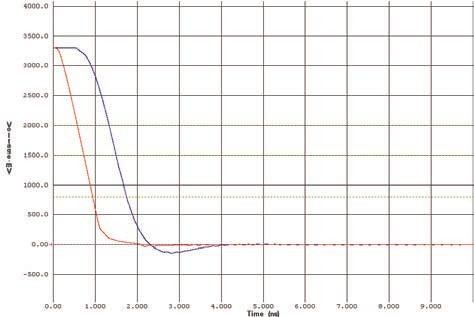

Obr. 2 Průběh signálu na výstupu (červená) a připojeném vstupu (modrá)

Potom je již možné spustit virtuální osciloskop, na kterém je znázorněn časový průběh signálu jak na výstupu, tak na připojeném vstupu pro jejich vzájemné porovnání. Na obr. 2 je vidět průběh obou signálů, jak se jeví při jednorázové změně stavu signálu z 1 na 0 (lze nastavit více možností, například hodiny s určitou frekvencí). Z obrázku, kde červená představuje průběh signálu na výstupu a modrá na vstupu, je patrné, že signál se dostává na připojený vstup s malým zpožděním, značným překmitem (více než –1 V) a následným zakmitáváním. Při napájení 3,3 V je u připojené součástky jisté, že nebude fungovat správně.

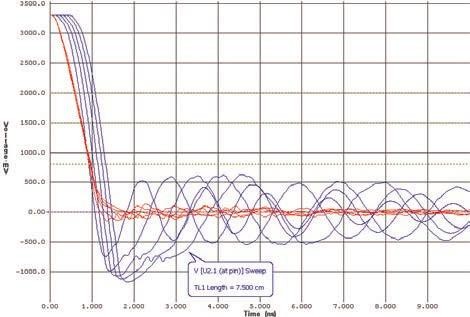

Obr. 3 Průběh signálů pro délky plošného spoje 15–75 mm

Existuje několik možných řešení vzniklé situace. Jako první se nabízí zkrácení délky plošného spoje. Abychom si mohli udělat dobrý závěr o vlivu délky na konkrétní plošný spoj, můžeme v programu provést tzv. Sweep analýzu pro několik různých délek najednou, řekněme v rozsahu 25 až 75 mm. Z výsledku na obr. 3 je vidět, že i když se s kratší délkou výsledek zlepšuje, není dosaženo potřebného řešení. Délka plošného spoje by musela být zkrácena na velmi malou hodnotu v rozsahu několika milimetrů, aby byl výsledek uspokojivý, což zřejmě není prakticky proveditelné. Je tedy zřejmé, že pro daný spoj a použité součástky bude nutné hledat jiné řešení.

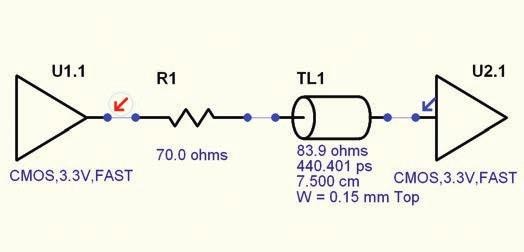

Obr. 4 Přidání rezistoru do zapojení

Nejčastějším řešením problému s přenosem signálu plošným spojem je použití sériového rezistoru těsně za výstupem. Existují ovšem i jiné možnosti, např. použití pull-up nebo pull-down rezistoru, kondenzátoru a další, se kterými umí program LineSim také pracovat. Do spoje se v zapojení přidá symbol rezistoru s přednastavenou hodnotou např. 70 Ω (obr. 4). Opětovná analýza přenosu signálu ukáže, že průběh signálu na připojeném vstupu se podstatně zlepšil (obr. 5), ovšem za cenu většího zpoždění. Hodnota 70 Ω nemusí být optimální, a tak je možné provést Sweep analýzu pro určitý rozsah hodnot, např. 50–80 Ω, a z nich vybrat tu nejvhodnější. Jiným možným řešením je využití pomocníka v programu, který sám provede analýzu dané situace a navrhne řešení – v tomto případě program navrhl sériový rezistor 62 Ω, při kterém zakmitávání na vstupu prakticky zmizí.

Obr. 5 Průběh signálů se sériovým rezistorem 70 Ω

Pokud by zvětšené zpoždění signálu na vstupu představovalo problém z hlediska funkce obvodu, potom by bylo možné přistoupit ke kombinaci zkrácení max. délky plošného spoje (např. 25 mm) a použití sériového rezistoru s odpovídajícím odporem. Další možností by bylo analyzovat situaci, kdy je daný plošný spoj umístěn na jiné vrstvě desky, např. blíže k zemnicí vrstvě.

Problematika zajištění dobrého přenosu signálu plošným spojem bývá často spojována i s dodržením určité impedance plošného spoje. Protože program LineSim průběžně přepočítává impedanci spoje, je právě tato analýza ve schematickém zapojení tou důležitou, protože dává návrháři konkrétní požadavky na provedení plošného spoje. Impedance plošného spoje se mění s jeho šířkou a umístěním na různých vrstvách desky.

Obr. 6 Analýza obvodu včetně přechodu přes via otvory

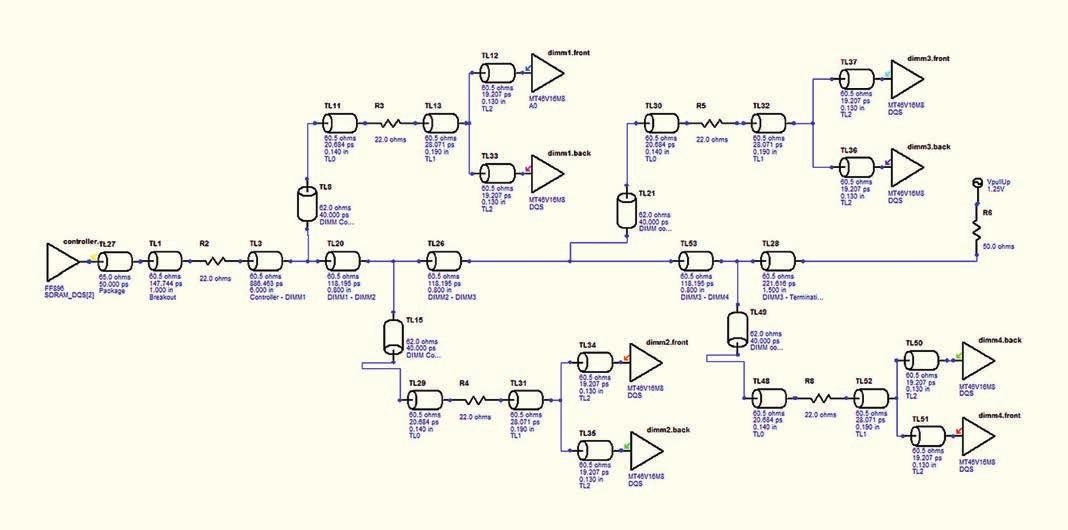

Praktické provedení plošného spoje ovšem není vždy tak jednoduché, jak je znázorněno na obr. 1, kde jde spoj od zdroje signálu přímo k připojenému vstupu. Plošný spoj může přecházet z jedné vrstvy do druhé, nebo dokonce přes konektor na jinou desku. Stejně tak signál z jednoho výstupu může napájet několik připojených vstupů. Tyto i další situace ovlivňují přenos signálu a i v takových případech je analýza možná. Na obr. 6 je zachyceno zapojení připravené pro analýzu obvodu včetně vlivu via otvorů, zatímco na obr. 7 je příklad zapojení pro analýzu obvodu s DDR pamětí.

Obr. 7 Zapojení pro analýzu obvodu s DDR pamětí

Kromě analýzy přenosu signálu plošným spojem lze provést i analýzu přeslechů a EMC. U přeslechů je potřeba definovat, který spoj se bude chovat jako zdroj přeslechu (agresor) a který spoj by mohl být negativně ovlivněn (victim), jejich vzájemné mezery a vrstvy desky, na kterých jsou položeny. Výsledkem bude opět doporučení pro návrháře: délky a šířky plošných spojů a vrstvy pro jejich položení při daném složení vrstev desky. U analýzy EMC se zjišťuje vyzařování daného spoje a nalezené optimální řešení je potom doporučením pro návrh desky.

Program LineSim umožňuje velmi jednoduše nastavit různé situace a provést jejich analýzu. Výsledkem jsou doporučení pro návrháře desky – maximální délka plošného spoje a jeho šířka, použitá vrstva při daném složení vrstev desky apod. Pokud je potřeba použít přizpůsobovací člen, jako je např. sériový rezistor, potom je ten i se svojí optimální hodnotou doplněn do schematického zapojení, a tím i automaticky přenesen do návrhu desky.

I když se Signal Integrity analýzy prováděné na zjednodušeném schematickém zapojení opírají pouze o předpokládané provedení na desce, dodržení výsledných doporučení při návrhu desky zajišťuje s velkou pravděpodobností podobné výsledky i na hotové, navržené desce.

Jak již bylo uvedeno, je také možné provádět analýzy nikoli ve schématu, ale na již navržené desce (program Hyperlynx BoardSim). Pochopitelně, že analýza přenosu signálu, přeslechů a EMC na navržené desce má své opodstatnění, protože poskytne skutečný obrázek o chování jak jednotlivých spojů, tak případně i celé desky, a to buď interaktivně, nebo automaticky. Cílem této analýzy je ověření správnosti navržené desky ještě před jejím zadáním do výroby (byť jenom v prototypovém provedení).

Oba programy, Hyperlynx LineSim i BoardSim, jsou k dispozici samostatně, nebo jako součást programů PADS ES. Podrobnější informace najdete na webových stránkách www.mentor.com.