V tomto již třetím pokračování seriálu o modulu SQM4-ZY7 a platformě Zynq®- -7000 Xilinx® All Programmable SoC podnikneme první kroky s nástrojem Xilinx Vivado a začneme pracovat na návrhu periferie pro řízení signálů displeje. Cílem je navrhnout logiku řadiče v jazyce Verilog tak, aby jej bylo možné použít se všemi typy a rozměry displejů, které jsou dodávány v rámci prototypové platformy SQM4-EasyBoard.

Termín „řadič“ je možná v našem případě trochu nadnesený, protože si neklademe za cíl navrhnout plnohodnotný zobrazovací prvek se všemi možnostmi. Pro demonstraci postupu tvorby a syntézy periferií pro platformu Zynq bude zcela stačit obvod, který vhodným řízením digitálních signálů displeje dosáhne zobrazení šachovnicového vzoru ve zvolené barvě.

Před prvním spuštěním nástroje Vivado, ve kterém provedeme konfiguraci Procesorového Systému (PS) i návrh a syntézu Programovatelné Logiky (PL), je důležité do nástroje vložit podporu modulů SQM4-ZY7. Tato úprava je velmi jednoduchá, spočívá pouze v nakopírování několika konfiguračních XML souborů z balíčku SQM4 do instalační složky Vivado. Soubory a detailní instrukce jsou k dispozici uživatelům modulu na stránkách http://www.sqm4.com.

Po spuštění nabídne aplikace Vivado založit nový projekt s pomocí přehledného průvodce, ve kterém krok po kroku zvolíme název projektu, projektovou složku, typ projektu „RTL Project“ a cílovou platformu Zynq (obr. 1). Díky upravené instalaci najdeme v průvodci předvolby připravené na míru všem podporovaným modulům SQM4.

Nově založený projekt je prázdný, bez jakýchkoliv zdrojových nebo konfiguračních souborů. Prvním krokem pak může být vytvoření tzv. „Block Designu“ (BD), což je prostor pro grafický návrh procesorového systému PS včetně jeho propojení se syntetizovanými periferiemi a dalšími částmi PL. Pro jednoduchost se v našem prvním projektu nebudeme příliš zabývat tím, kde jednotlivé soubory vznikají, a budeme volit možnost umístění „Local to Project“, tedy v podadresářích v rámci hlavní projektové složky. V profesionálních aplikacích se ovšem doporučuje oddělit projektové soubory od zdrojových kódů i od souborů grafického blokového návrhu. To je praktické nejen pro udržení pořádku a přehlednosti, ale především při po užití verzovacích nástrojů, jako jsou SVN nebo GIT. Ukázkový projekt dostupný zákazníkům na stránkách sqm4.com dělí adresáře na projektovou složku „viv“, složku „hdl“ se zdrojovými soubory a na složku „sw“ se softwarovými projekty.

Pro účely naší jednoduché aplikace bude zcela stačit jeden „Block Design“, který vytvoříme a nazveme krátce „ps“ (obr. 2).

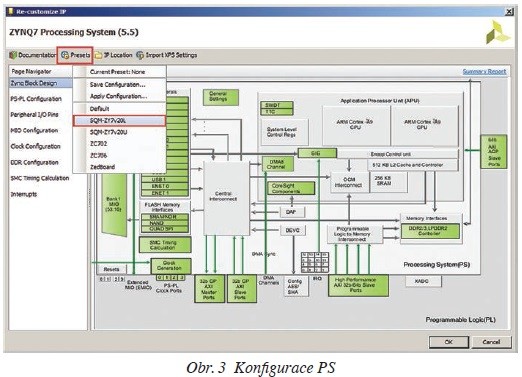

Do blokového návrhu se vkládají grafické objekty, tzv. IP (= Intellectual Property), reprezentující funkční bloky v PS nebo PL. Volbou „Add IP“ je možné procházet bohatou knihovnou hotových IP bloků poskytovaných buď přímo firmou Xilinx, nebo některým z jejích partnerů podporujících univerzální datový formát nazvaný IP-XACT. Ve stejné knihovně se nakonec objeví i naše vlastní vytvořená periferie. V prvním kroku nás ovšem zajímá především blok „ZYNQ7 Processing System“, který reprezentuje kompletní procesorový systém platformy Zynq včetně „pevných“ periferií, jako např. UART, SPI, I2C, CAN nebo řadiče pamětí DDR. Konfigurace tohoto bloku je poměrně komplexní a zdlouhavý proces, a to i přes to, že se provádí v uživatelsky přívětivém grafickém prostředí. Konfigurace je totiž z velké části závislá na návrhu DPS, na délkách spojů k obvodům DDR i na konkrétním využití vstupně výstupních periferních pinů, tzv. MIO.

Díky tomu, že modul SQM4-ZY7 představuje již téměř hotové řešení s pevně daným a známým zapojením většiny pinů s vyhrazenou funkčností, je konfigurace PS v našem případě naopak jednoduchá a na cílové aplikační desce (EasyBoard) nezávislá. Navíc, díky modifikované instalaci Vivada, máme veškeré nastavení našeho modulu již integrované a připravené k použití přímo jako konfigurační předvolbu – tzv. „Preset“. Konfigurace celého bloku je tedy otázkou jen několika kliknutí myši. Ve schématu pak můžeme blok propojit se vstupními a výstupními porty a dále připravit pro budoucí propojení s dalšími IP (obr. 3).

Na tomto místě bude možná dobré ještě připomenout minulý díl seriálu a vysvětlit, co vlastně v BD schématu tvoříme. K bližšímu popisu se asi dostaneme příště, kdy do diagramu „ps“ vložíme další bloky a propojíme jej s kódem tzv. top-level modulu. Do té doby snad vystačíme se znalostí prostého faktu, že celý BD, pokud v něm definujeme vstupní a výstupní porty, může figurovat jako plnohodnotný modul kompatibilní se syntaxí jazyka Verilog. V libovolném nadřazeném modulu pak tedy můžeme vytvářet jeho pojmenované instance, propojovat je a konfigurovat, stejně jako jsme to předvedli dříve s čítačem simple_counter.

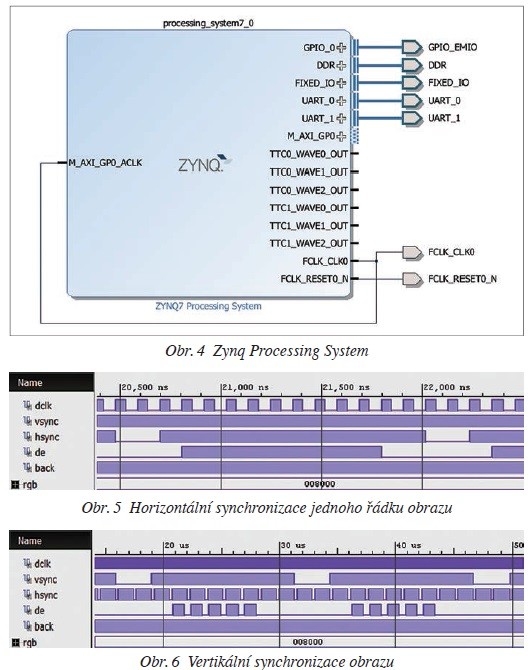

Po vytvoření potřebných výstupních portů by měl náš „ps“ diagram vypadat tak jako na obrázku 4. Tento základní návrh budeme postupně rozšiřovat o sběrnici AXI a naši „šachovnicovou“ periferii, kterou vytvoříme v rámci odděleného Vivado projektu. Nejprve se ale musíme lépe podívat na signály, které displej potřebuje ke své činnosti.

Displeje použité s prototypovou platformou EasyBoard používají „klasické“ řízení velmi podobné standardnímu analogovému VGA rozhraní, ovšem v digitální podobě. Řídicí signály jsou synchronní vůči hodinovému taktu DCLK. Signál HSYNC startuje horizontální sekvenci jednoho řádku (obr. 5), která se skládá ze tří fází:

Signál VSYNC pak startuje vertikální synchronizaci obrazu (obr. 6), opět rozdělenou do stejných fází jako horizontální. Místo jednotek DCLK se však vertikální synchronizace časuje celými periodami HSYNC:

Jak je zřejmé, bude pro implementaci řadiče stačit poměrně jednoduchá sada čítačů a dvou stavových strojů vhodně zkombinovaná s řídicí logikou. Než se v příštím díle pustíme do programování, mohli bychom si ještě naplánovat, jaké signály bude řadič potřebovat a jaké konfigurační parametry bychom chtěli mít možnost nastavovat z obslužného softwaru. IO signály řadiče:

Periferní registry:

V příštím díle rozebereme Verilog kód šachovnicového řadiče displeje. Do projektu přidáme i jednoduchou komponentu pro obsluhu sběrnice AXI s návazností na periferní registry, jejichž prostřednictvím bude náš software zobrazování na displeji konfigurovat. Pomocí nástroje Vivado pak pro celou periferii připravíme komponentu ve formátu IP-XACT, vložíme ji do blokového diagramu a připojíme k procesorovému systému. Cílem by mělo být funkční řešení připravené pro vývoj softwaru s nástrojem Xilinx SDK.