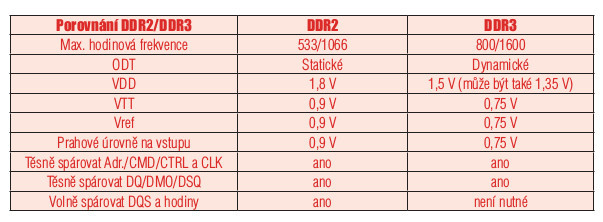

Tento článek popisuje vyzkoušená a ověřená pravidla pro návrh desek plošných spojů s paměťmi DDR, DDR2 a DDR3 (dále DDRx), včetně příslušných metod.

Před zahájením návrhu desky je důležité správně navrhnout uspořádání jejích vrstev. Má-li být dosaženo nejlepších výsledků, je třeba vzít v úvahu:

Technologická pravidla vycházejí z minimální rozteče vývodů použitých BGA součástek, čímž určují největší dovolené rozměry plošného spoje, mezery a via otvoru při minimalizaci výrobních nákladů desky. Obvykle se požaduje technologie 4/4 mil (0,1 mm šířka/0,1 mm mezera) s via otvory 20/8 mil (0,5 mm ploška/0,2 mm otvor).

Jakmile budou tato pravidla stanovena, určete nutné uspořádání vrstev desky pro dosažení požadované charakteristické impedance (Zo) a rozdílové impedance (Zdiff). Tyto hodnoty jsou pro DDRx Zo=50 a Zdiff=100 , zatímco pro DDR je Zo=60 . Mějte na paměti, že nižší impedance zvýší hodnotu dI/dt a dramaticky zvýší odebíraný proud, což není dobré pro rozvod napájení (PDN) a vyšší impedance vyvolá větší elektromagnetické rušení a návrh pak bude rovněž citlivější na vnější rušení. Proto je vhodným rozsahem Zo 50 až 60 .

Mějte také na paměti, že se na desce mohou používat diferenciální signály USB. V takovém případě je nutné, aby se impedance Zdiff rovnala 90 . Proto bude potřeba těmto signálům přizpůsobit šířku plošného spoje a mezery.

Jak ale zjistíte hodnoty Zo a Zdiff pro celé uspořádání vrstev desky při použití zavedených návrhových pravidel?

Řešení této úlohy vám usnadníme. Společnost In-Circuit Design Pty Ltd vyvinula Stackup Planner. Tento nový produkt vychází z oblíbené on-line kalkulačky impedancí (Impedance Calculator) společnosti In-Circuit Design, kterou využívají desítky tisíc techniků a návrhářů desek plošných spojů z celého světa již od roku 1996. Funkční demoverzi si lze stáhnout na www.icd.com.au.

Jak jistě víte, řadiče pamětí DDRx, FPGA nebo procesory mají mnoho různých požadavků na napájení. Nejprve je nutné identifikovat hlavní stejnosměrné napájecí zdroje a pro každý z nich vypočítat maximální odebíraný stejnosměrný proud. Může být například požadováno 5 A při zvýšení teploty desky o 20 °C, takže návrhová pravidla je třeba stanovit s ohledem na tento požadavek. Dalším problémem potom bývá nalezení cesty, kudy bude napájení přivedeno k BGA součástkám. To lze udělat za předpokladu, že se napájecí vrstva nepoužívá pro zpětnou cestu signálů z DDRx pamětí. Nejlepší je tyto hlavní obvody umístit přímo pod řadič.

Funkcí filtračního kondenzátoru je tlumit střídavé zvlnění na napájecím vedení. Když signály současně spínají, značně zvyšují odebíraný proud a stejnosměrný napájecí zdroj má sklon superponovat do tohoto proudu zvlnění. A aby to bylo ještě horší, nejnovější integrované obvody jsou velmi citlivé na rušení v důsledku sníženého napájecího napětí a přítomnosti velkého počtu možných generátorů šumu.

Lokální blokovací kondenzátory dodávají součástkám okamžitý proud (s různými frekvencemi), dokud napájecí zdroj nezareaguje. Jinak řečeno, chvíli to trvá, než se dostane proud od napájecího zdroje do konečného místa, a to kvůli indukčnosti plošného spoje a/nebo vodičů vedoucích k řídicím obvodům.

Nejlepší je řídit se doporučeními výrobce čipu o počtu, hodnotách a rozmístění těchto kondenzátorů. I když umísťovat tři nebo čtyři blokovací kondenzátory u každého napájecího vývodu je dost nešikovné řešení. Podrobněji se tomu budeme věnovat v kapitole o rozmístění součástek.

Návrháři obvykle věnují značnou pozornost zajištění toho, aby plošné spoje s přizpůsobenou délkou byly položeny v přesné délce od výstupu k vývodu DRRx součástky, ale vůbec je nezajímá zpětná cesta pro návrat signálu. Proud přece teče tam a zpět. Bude-li signálu trvat déle, než se jeho proud vrátí do řídicího obvodu (například kolem mezery ve vrstvě), pak vznikne časový posuv mezi kritickými časovacími signály.

A tak až budete plánovat uspořádání vrstev desky, myslete na to, přes kterou vrstvu nebo vrstvy (buď napájecí, nebo zemnicí) se bude realizovat návrat kritických signálů, a zajistěte, aby byly bez překážek.

Specifikace pamětí DDRx lze stáhnout ze stránek www.jedec.org. Zpočátku bude dosti zdlouhavé probírat se mnoha stránkami požadavků na rozvrhy časování, spoji s přizpůsobenou délkou, diferenciálními páry a zkráceními potřebných dob.

Specifikace JEDEC pro paměti DDRx:

DDR JESD 79F

DDR2 JESD79-2E

DDR3 JESD79-3D

Tyto paměti jsou typu SDRAM a používají architekturu DDR (Double Data Rate) k dosažení vysoké rychlosti provozu tím, že přenáší dvě datové informace v jednom hodinovém cyklu na I/O vývodech.

Pokyny pro návrhy s DDR – kritická omezení:

V úvahu je potřeba vzít i další omezení:

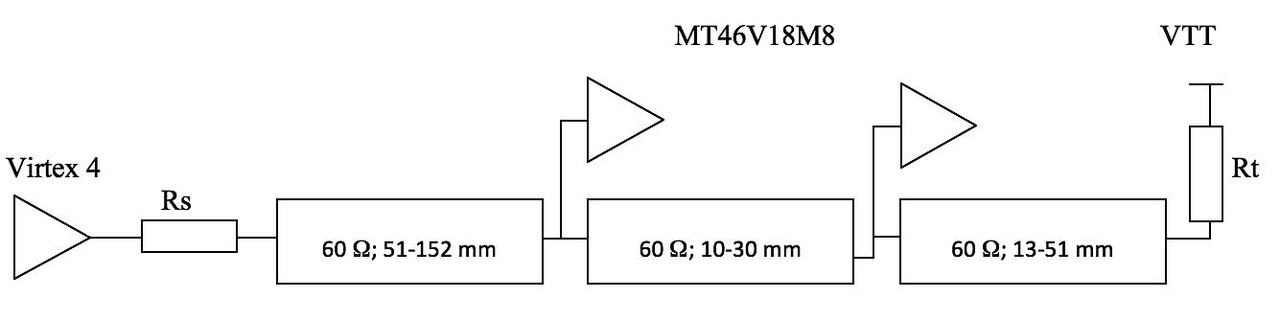

Obr. 1 Adresové, datové a ovládací spoje mohou vyžadovat sériové a VTT zakončení

Hodnoty a umístění sériových a VTT pull-up rezistorů pro datové, adresové a ovládací spoje závisí na vzdálenostech mezi připojenými vstupy, počtu připojených vstupů a uspořádání vrstev desky a nejlépe se určují simulací. Sériový zakončovací člen nemusí být nutný, je-li použit pouze jediný SDRAM a plošný spoj je krátký.

Vrstvy desky se spoji je potřeba volit tak, aby každá síť spojů (net) měla společnou referenční vrstvu (vrstvy) pro zpětnou cestu signálu a byla routována uvnitř desky (je-li to možné) kvůli potlačení elektromagnetického rušení. U každé desky s velmi rychlými obvody je nutné analyzovat přeslechy, aby se potlačilo rušení.

Pokyny pro návrhy s DDR2 – kritická omezení:

V úvahu je potřeba vzít i další omezení:

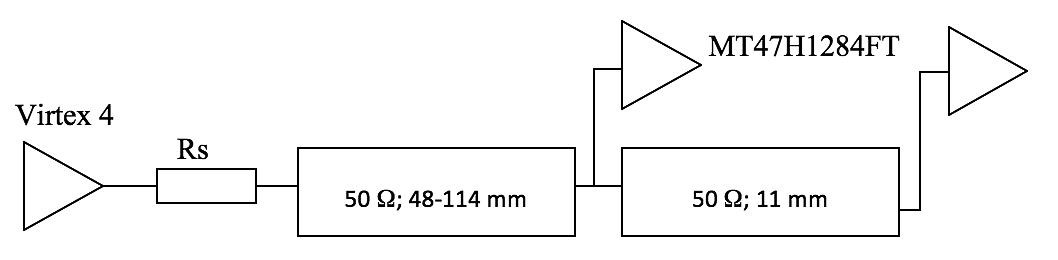

Obr. 2 Obvod DQ (datový) nemá VTT zakončení

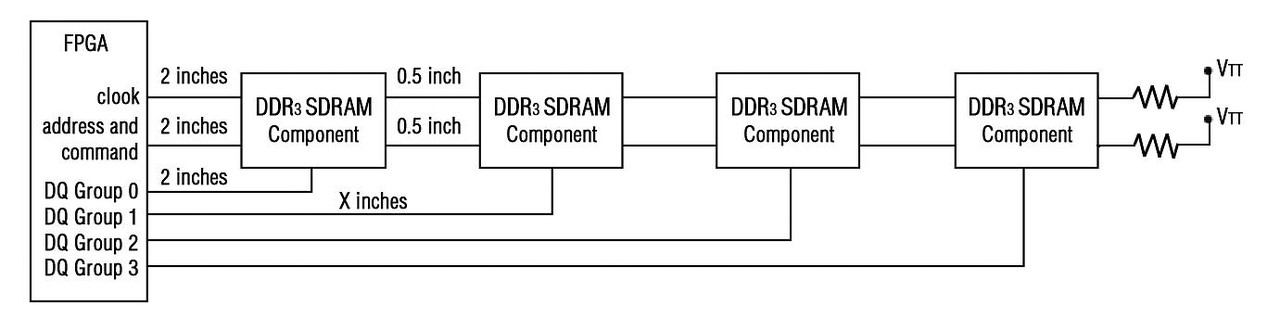

Jeden z hlavních rozdílů mezi paměťovými moduly DDR2 a DDR3 SDRAM spočívá v použití tzv. levellingu. Aby se zlepšila integrita signálu a podpořily operace s vyšší frekvencí, výbor JEDEC definoval schéma „fly-by“ pro zakončení využívané hodinovými, ovládacími a adresovými signály. „Fly-by“ topologie redukuje spínací šum (SSN) tím, že záměrně vyvolává posuv doby přenosu signálu mezi daty a synchronizací v každém čipu/modulu DRAM, což vyžaduje, aby tento posuv kompenzovaly řadiče úpravou časování v jednotlivých obousměrných párech datových linek.

Během zápisu jsou skupiny DQS spouštěny v různých okamžicích, ve shodě s hodinovými impulzy přicházejícími do DIMM a musí být přitom dodržen parametr časování mezi hodinami paměti a obvodem DQS, definovaný jako tDQSS s hodnotou v rozsahu ±0,25 tCK.

Návrhový proces lze zjednodušit díky využití nové vyrovnávací funkce DDR3 a integrovaných řadičů. „Fly-by“ topologie uzavřeného obvodu zvyšuje složitost datové cesty a návrhu řadiče, aby umožnila vyrovnání, přitom však značně zvyšuje výkon a usnadňuje návrh desek pro moduly DDR3.

Pokyny pro návrhy desek s moduly DDR3 – kritická omezení:

Obr. 3 Topologie DDR3 využívající levellingu

V úvahu je potřeba vzít i další omezení:

Analýza provedená před návrhem desky má velký význam. Předběžná simulace se používá k včasnému zjištění a odstranění problémů s integritou signálu a k předefinování routování, optimalizaci hodin, kritických signálových topologií a všech zakončení před vlastním návrhem desky.

Jak již bylo uvedeno, hodnota a umístění sériových a VTT pull-up rezistorů pro datové, adresové a ovládací signály závisí na vzdálenostech mezi připojenými vývody, na počtu připojených vstupů a uspořádání vrstev desky, což se nejlépe určuje za pomoci simulace. Sériový zakončovací člen nemusí být nutný, pokud se používá jediný modul SDRAM a plošný spoj je krátký – ale jak to zjistíte, když navržené uspořádání nebudete simulovat?

Obvyklým postupem je pokusit se udržet SDRAM co nejblíže k řadiči, ale občas to není kvůli jiným omezením možné. Také platí, že pokud se používají dva nebo více čipů SDRAM, nutnost zakončovacích členů pro delší signálová vedení se stává obtížnějším úkolem. Ale kde mají být tyto členy umístěny a jaké hodnoty je třeba použít?

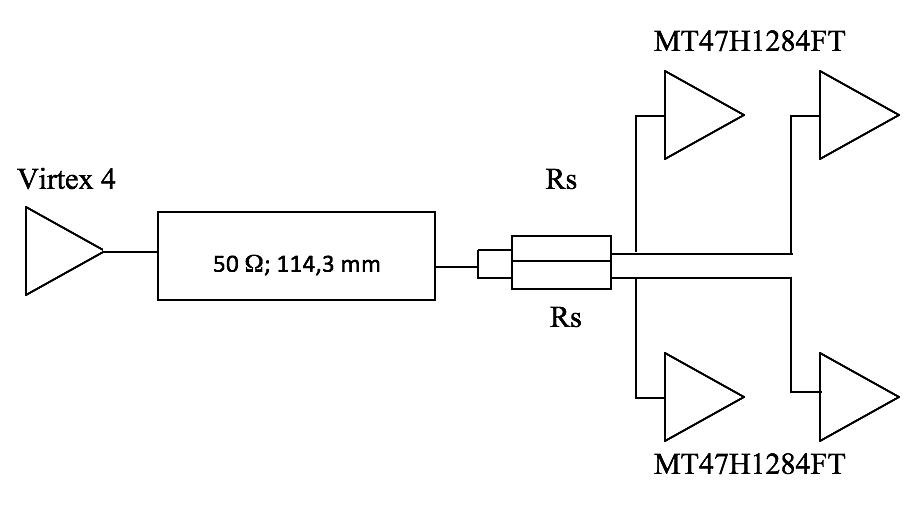

Sériový zakončovací člen by měl být normálně umístěn blízko výstupu řídicího obvodu. Je však překvapující, že ve výše uvedeném případu bude integrita signálu mnohem lepší při větší vzdálenosti (114 mm) od řídicího obvodu. Signál je pak rozdělen pomocí dvou sériových odporů a přiveden do každé skupiny pamětí DDR2 SDRAM (obr. 4). Toto řešení je neobvyklé, ale demonstruje význam simulace pro dosažení nejlepšího možného výsledku. Díky této metodě proběhne návrh maximálně rychle a není nutné jej předělávat.

Obr. 4 Rozdělení signálů přes 2 rezistory Rs

Pokud jste provedli úplnou analýzu před návrhem desky, podstatou správného rozmístění je pak dodržení omezení stanovených pomocí pravidel pro délku spojů a rozmístění. Sériové zakončovací členy jsou obvykle umístěny do součástky typu RESNET 1206 (pouzdro se 4 rezistory) nebo 0402 na spodní straně desky, protože horní stranu obvykle zabírají velké aktivní prvky.

Blokovací kondenzátory je třeba umístit přímo pod aktivní prvek a jeli to možné, připojit napájecí vývody spoji o šířce 0,5 mm, aby se zmenšila indukčnost. Někdy lze použít via otvory vedené od napájecích vývodů pouzdra BGA s malou roztečí jako jednoho vývodu pro blokovací kondenzátor 0402 (oktagonální pájecí ploška je umístěna přímo na horní stranu via otvoru, druhá oktagonální pájecí ploška je zemnicí).

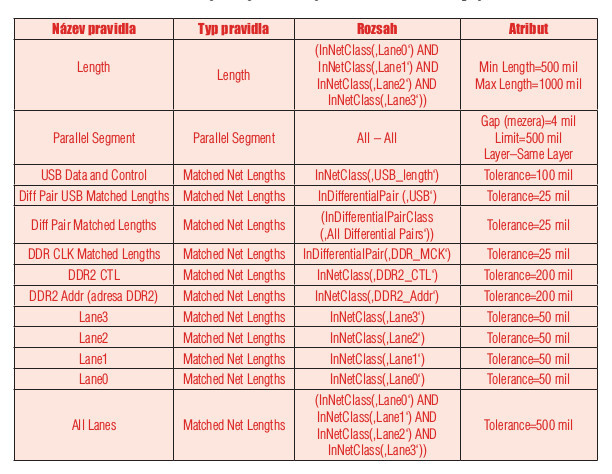

Určení optimálních návrhových pravidel pro návrh desek může být sice poněkud pracné, ale jakmile je provedeno, po prvním návrhu je můžete zpravidla exportovat i do dalších návrhů a ušetřit tak čas. V tabulce je uveden příklad pravidel pro návrh desek s vysokorychlostními paměťovými moduly DDR2 pomocí aplikace Altium Designer.

Je-li to možné, obvykle zmenšujeme toleranci uvnitř obousměrných datových linek (Data Lanes) 0–3 na 0,63 mm, abychom dosáhli těsnějšího spárování, ačkoli specifikace JEDEC je 1,25 mm. Speciální pravidla pro návrh desky s velmi rychlými obvody (high speed design) by měly mít v hierarchii návrhových pravidel nejvyšší prioritu.

Konečná analýza po návrhu desky zahrnuje simulaci všech sítí spojů v dávkovém režimu. Kontroluje integritu signálu a upozorňuje na přeslechy a problematická místa z hlediska EMI. Pečlivým prostudováním výsledných výpisů analýz, lze odhalit jakékoli problémy, které mohou nastat.

Simulace v dávkovém režimu upozorňuje na:

Je nutné projít tyto body jeden po druhém a rozmyslet si, zda není nutné provést nějaké kroky. Může například dojít k tomu, že dlouhý signál „Reset“ nebo signál vedený ke statickému pull-up rezistoru je hlášen jako příliš dlouhý, ale my tato konkrétní varování většinou ignorujeme. Ale může se vyskytnout i situace, že kritický signál je veden příliš dlouhou trasou, kterou je třeba zkrátit – a tím je nutné se zabývat.

Přeslechy jsou v návrzích s velmi rychlými obvody velmi časté. Důvodem je přehuštěný prostor, protože signály je nutné stěsnat do malého prostoru. Přeslechy lze minimalizovat zvětšením mezer mezi spoji a přiblížením signálové vrstvy k referenční vrstvě. Je třeba pokusit se udržet tloušťku 0,075 mm pro prepreg, aby byly signály těsněji svázány s touto vrstvou. Může být rovněž nutné přidat do souboru vrstev další vrstvy pro oddělení rušivých signálů-agresorů. Pronikání rušivých signálů může též omezit kolmé vedení spojů v sousedních signálových vrstvách.

Problémy s přeslechy mohou způsobit přerušovaný provoz v důsledku rušivých časovacích impulzů a rušení, což výrazně snižuje spolehlivost výsledného produktu. A tak je nejlepší řešit tyto problémy přímo u zdroje.

Bude-li odvedena dobrá práce při vedení velmi rychlých signálů na vnitřních vrstvách a daleko od okrajů desky, elektromagnetické rušení (EMI) by mělo být minimální. Pokud však problém s EMI nastane, je nutné pro jeho vyřešení vyzkoušet jiné strategie vedení spojů. Během návrhového procesu lze hodnotit elektromagnetickou kompatibilitu podle norem FCC, CISPR a VCCI pro třídy A a B – jen samotné toto hodnocení vám ušetří mnohá opakování návrhu.

Všechny kritické velmi rychlé signály je nutné individuálně zkontrolovat. Doby přenosu signálu musí odpovídat specifikaci a „eye diagramy“ musí mít „oči doširoka otevřené“.

Advanced Design for SMT – Barry Olney, In-Circuit Design Pty Ltd

Specifikace JEDEC JESD 79F, JESD 79-2E & JESD79-3D

Altera Board Layout Guidelines, EMI_Plan_Board