Společnost ON Semiconductor je producentem komplexních řešení smíšených obvodů pro aplikace z oblasti automobilového průmyslu, komunikací, výpočetní techniky, spotřební a průmyslové elektroniky, LED osvětlení, lékařských aplikací, vojenského/leteckého průmyslu a napájecích zdrojů. Společnost poskytuje špičkové technologie FSI, BSI i skládání waferů, spolu s množstvím odborných informací z oblasti návrhu nízkošumových a vysokorychlostních mixed-signal aplikací, pouzder a optiky či aplikací z oblasti zpracování obrazu a systému pro zobrazení. Prvky polovodičových obrazových snímačů s variabilním rozlišením, optickým formátem a snímkovou frekvencí jsou používány téměř v každé běžné aplikaci vyžadující zpracování obrazu; včetně automobilového průmyslu, monitorování a bezpečnosti, průmyslu/internetu věcí, zdravotnických, vesmírných a spotřebitelských trhů. Firma je opravdu typu „one-stop-shop“ pro všechny výrobce fotoaparátů, kteří hledají ideální řešení pro širokou škálu zákaznických požadavků.

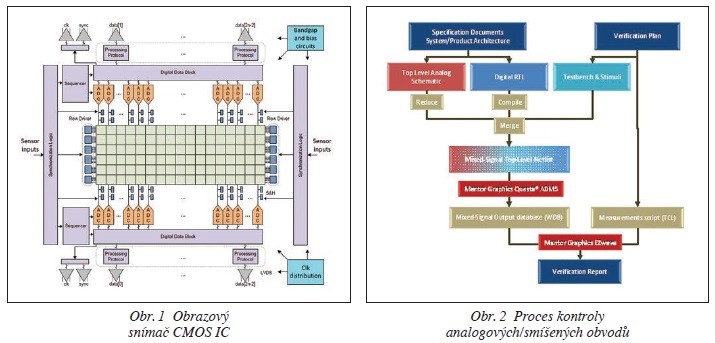

Obrazové senzory musí splnit náročné požadavky z pohledu funkčnosti obvodů smíšených signálů. Obrazy mohou být velmi velké a složité analogové/smíšené obvody obsahující velké množství opakujících se struktur; například analogově-digitálních převodníků (ADC) a pixelových polí. Obrázek 1 ilustruje rozsáhlý obrazový senzor zahrnující velké množství analogových i digitálních obvodů: tisíce ADC, více než 100 LVDS kanálů (1 Gbps) a 5 milionů digitálních hradel.

Analogové a smíšené návrhy obvodů tvoří užší spojení analogového a digitálního obsahu více než kdy předtím. Je známo, že vzhledem k narůstající složitosti konstrukce, včetně dalších procesů a velkého množství zařízení, je úplné ověření analogového/smíšeného čipu příliš náročné, aby jej bylo možné simulovat v rozumném čase. Ověření úplného obrazového snímače na nejvyšší úrovni je téměř nemožné.

Nicméně však v praxi existuje celá řada důvodů, proč je ověření nejvyšší úrovně snímače povinné. Primárním cílem je samozřejmě ověření funkčnosti. Pokud se provede kontrola a kvalifikace každého analogového a digitálního bloku individuálně s ohledem na jeho dané specifikace, je možné zákazníkovi garantovat, že při použití těchto bloků bude kamera pracovat podle očekávání.

Stále zůstává mnoho otázek pro výběr správné metodiky pro kontrolu složitých analogových/smíšených integrovaných obvodů, jako je právě obrazový snímač.

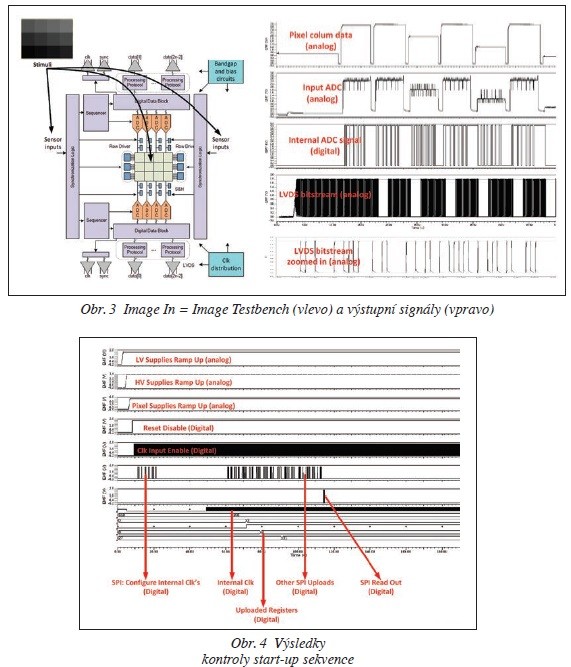

Vzhledem k tomu, že pole pixelů je obvykle velmi velké, využívají konstrukční týmy při funkční simulaci nejvyšší úrovně pole, které má podmnožinu řádků, sloupců a souvisejících řídicích a čtecích obvodů. Kompromisu mezi časem simulace a přesností je dosaženo pomocí simulace malé matrice, jejíž výsledky jsou použity pro predikci funkce velkých matic.

Na základě tohoto přístupu i daných omezení navrhl Wiet Vroom, konstruktér ON Semiconductor, následující plně automatizovaný cyklus šesti kroků.

Obrazové snímače jsou vyrobeny z velkého množství opakujících se bloků. Proto je poměrně snadné vyjmout jen pár bloků od každého typu, několik sloupců ADC, několik ovladačů řádek atd. To se provádí automaticky pomocí skriptu v Perlu, který začíná od netlistu na nejvyšší úrovni a komentuje všechny instance, které se následně nepoužijí.

Makefile generátor zajišťuje automatickou kompilaci VHDL, Verilog a smíšených VHDL/ Verilog návrhů.

Sloučení analogového netlistu s digitálním RTL se provádí rovněž automaticky, pomocí skriptu, který nahradí prázdné schematické buňky s digitálním počítadlem prvků.

Plán ověřování dokumentů se využívá ke generování dodávek, vstupů pixelů a časování signálů (řízení, hodiny a sériové periferní rozhraní).

Simulace nejvyšší úrovně analogového/smíšeného návrhu je konečně provedena v rámci Questa ADMS, který tvoří silný nástroj s vysokou flexibilitou, snadno kombinující popis digitálních a analogových RTL úrovní tranzistorů.

Na závěr je výstup binární databáze (WDB) automaticky postzpracován skriptem EZwave™ TCL s analýzou bitového toku a hodinových signálů LVDS (lowvoltage differential signaling) a automatickým zápisem výstupního obrazu do souboru.

Celý postup je znázorněn na obrázku 2. Proces při maximální úrovni kontroly nabízí plnou automatizaci, nejlepší kompromis mezi přesností a rychlostí při současné minimalizaci rizikových faktorů a další práce. Modelování AMS nebylo třeba použít (VHDL-AMS, VHDL-RN a Verilog-AMS).

Obrazová divize společnosti ON Semiconductor byla, s vysokým stupněm automatizace a bezpečnosti, schopna zajistit přesnější kontroly analogových/smíšených obvodů na nejvyšší úrovni (obr. 3 a obr. 4). Pouze za pomoci Questa ADMS a EZwave řešení od společnosti Mentor Graphics, bez použití jakýchkoliv AMS behaviorálních modelů, což v praxi eliminuje čas i chyby v provedení přesných modelů. Ke kontrole nejvyšší úrovně je potřeba použití 8 CPU se 100 GB paměti. Vzorová simulace smíšeného obvodu v Questa ADMS trvala tři až čtyři dny. Průměrný SPICE netlist obsahoval 716 tisíc MOS prvků a 320 tisíc uzlů. S využitím této metodiky byly úspěšně ověřeny již dva obrazové snímače. Třetí a čtvrtý jsou na cestě.