Pro někoho může být stále překvapením, že v dnešní době jsou sériové linky rychlejší než ty paralelní. Tento paradox vznikl historicky, jelikož se vývoj soustředil na sériový přenos dat, protože vzdálenosti, na které se vyplatí použít paralelní přenos, se zkracují s rostoucí rychlostí komunikace. Paralelní transfer potřebuje vedení pro každý bit zvlášť (cena a prostor pro vedení) tak, aby se vzájemně neovlivňovaly (vzájemná kapacita, přeslechy), a potřebuje synchronizovat velké množství dat.

Sériové linky dominovaly větším vzdálenostem, ale se zrychlováním složitějších obvodů na jejich vstupu (serializérů) a výstupu (deserializérů) vytlačují paralelní linky už i z kratších vzdáleností. Provedení serializace/deserializace (odtud SerDes kanál) je klíčem k rychlosti, a zřejmě proto bylo vyvinuto více standardů k její realizaci (PCI-Express, USB, Bluetooth, RS-232, SPI, I²C, …). Jednotlivé specifikace se však mohou velmi lišit i v určení základních pojmů, jako například jitter (kolísání, nestabilita zdroje frekvence).

Se zvyšujícími se požadavky na komunikaci a při neustálém rozšiřování standardů je obtížné dodržet specifikace, správně navrhnout a ověřit funkci SerDes kanálu. Pouze minimum návrhářů si pamatuje veškeré nároky a i po konzultaci s tištěnou dokumentací mnohým nezbývá než se obrátit na experta v oblasti elektromagnetické simulace.

Společnost Mentor, a Siemens business, proto rozšiřuje funkcionalitu sady programů HyperLynx pro simulace desek plošných spojů o technologii automatické extrakce SerDes kanálu a jeho analýzu. HyperLynx SERDES automatizuje kroky nutné před vlastní simulací, které je obyčejně potřeba dělat ručně: Rozdělí přenosovou cestu na části, které je nutné modelovat jako 2D a 3D pole, vygeneruje S-parametry pro části reprezentované ve 3D, propojí je s těmi ve 2D a exportuje model, který pomocí těchto parametrů popisuje celé propojení. Tento model lze použít pro analýzu ve frekvenční oblasti nebo ověření shody s předepsanými parametry jednotlivých standardů. Modely využívající S-parametry shodných bloků mohou být na desce použity vícekrát, což zrychluje následné simulace.

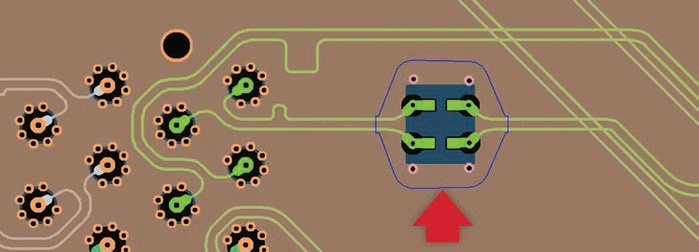

Obr. 1 3D oblast automaticky vytvořená v závislosti na dostupné cestě návratu signálu

HyperLynx SERDES Analysis kontroluje dodržení norem pro více než 25 protokolů, přičemž dokumentace každého z nich může obsahovat stovky stránek a není lehce dostupná, podobně jako IBIS-AMI modely nutné k ověření probíhající komunikace. SERDES Analysis usnadňuje pomocí průvodce simulaci USB 3.1, PCI-e 4.0, SATA 3.2, ethernetu a dalších sériových linek, přičemž nevyžaduje od návrháře desky podrobnou znalost jejich dokumentace. Zabudovanými modely chování lze nahradit potřebu IBIS-AMI a navíc tím zrychlit celý proces. HyperLynx na jejich základě, spolu s referenčním návrhem zkoumaného protokolu, pomáhá identifikovat optimální nastavení Decision Feedback ekvalizéru (DFE) nebo lineárního ekvalizéru (CLTE) a dalších parametrů.

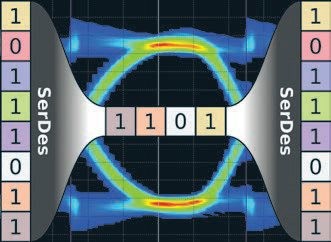

Obr. 2 Zobrazení serializace – deserializace

Většina analýz je prováděna ještě před vlastním položením spojů na desce a zahrnuje vytváření a ověřování geometrie spojů, vzorů průchodů deskou (prokovů), vyvádění a přivádění cest k Ball Grid Array (BGA) čipům, … Velké množství nastavitelných hodnot vytváří téměř nekonečnou množinu možností. Proto HyperLynx využívá přístup založený na vzorech jednotlivých variant, jejichž parametry lze měnit. Výsledky pro lehce odlišné hodnoty lze zobrazit v jednom výstupu pro identifikaci nejlepší varianty. Standardem zobrazování výsledků v programech HyperLynx je přehledný HTML formát.

S pomocí průvodce v SERDES Analysis zvládne analýzu kanálu v kratším čase a s menšími nároky na paměť i návrhář, který není expertem na elektromagnetickou simulaci, a to díky automatické extrakci a práci s modely.

(radek) @cadware.cz