IMAPS a rostoucí význam pouzdření v moderní mikroelektronice

Není pochyb o tom, že dominantní mikroelektronickou komponentou je polovodičový čip, který ve většině případů určuje charakter a vlastnosti daného elektronického obvodu či systému. Přitom polovodičové čipy jsou stále složitější a komplexnější, a potom také elektronické produkty jsou stále menší, výkonnější a sofistikovanější. To s sebou přináší nové požadavky na řešení pouzdření a propojování, jež vyžadují také nový přístup k návrhu a konstrukci moderních elektronických obvodů. Zde je nutné zvažovat stále více faktorů, což bez znalosti nových skutečností není možné v optimální míře. Moderní obvody a systémy jsou dnes většinou tvořeny heterogenními strukturami, které obsahují organické i anorganické materiály. V takových strukturách pak působí různé fyzikální a chemické jevy ovlivňující jejich spolehlivou funkci. Právě na tuto problematiku je zaměřena mezinárodní společnost IMAPS (International Microelectronics Assembly and Packaging Society), jejímž cílem je šíření nových poznatků z oblasti moderní konstrukce, montáže a pouzdření elektronických celků (www.imaps.org, www.imapseurope.org, www.imaps.cz).

Vývoj pouzdření

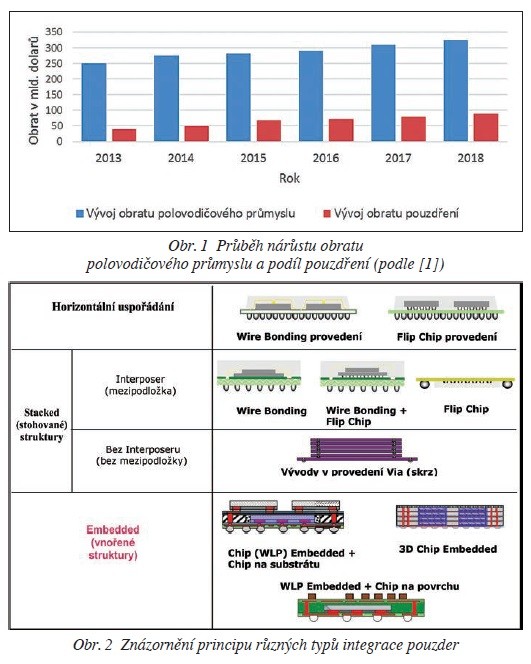

Role pouzdření v elektronice stále roste, a to nejen svým nenahraditelným významem, ale také objemem investic. V průběhu let 2010 až 2016 již přesáhl celkový obrat více než 330 miliard USD, přičemž pouzdření tvoří jednu sedminu z celkového obratu (přes 50 miliard dolarů). V této částce je téměř rovnoměrné procentuální rozložení mezi materiál a zařízení, které tvoří mírně vyšší částku, kolem 30 miliard USD. Na obr. 1 je znázorněn růst obratu polovodičového průmyslu v letech 2010 až 2016 spolu s nárůstem obratu v sektoru pouzdření. Z obrázku je patrné, že obrat v oblasti pouzdření se v průběhu posledních šesti let téměř zdvojnásobil.

Zajímavé jsou průzkumy provedené společností Yole Développement o vývoji trhu pouzdření. Zde se odhaduje nárůst výnosu vyspělých typů pouzdření o téměř 10 miliard USD od roku 2014 do roku 2020, především zaváděním Fan-Out WLP, 2.5D / 3D, Flip-chip a montáží holých čipů. Tyto pokročilé techniky pouzdření v současné době již tvoří 38 % z celkového objemu pouzdření (kolem 20 miliard USD) a očekává se nárůst podílu na 44 % v roce 2020.

Moderní řešení elektronického systému bezprostředně souvisí se způsobem pouzdření a také propojování. Pouzdro a způsob pouzdření rozhodují o dvou základních, ale ve většině případů také protichůdných vlastnostech pouzdra, kterými jsou jakost, resp. spolehlivost oproti ceně. Technologie výroby polovodičových čipů přesahuje svými možnostmi ostatní požadavky, a proto se pozornost soustředí na oblasti, jako jsou:

- Snižování nákladů

- Zvýšení výkonu

- Integrace funkcí

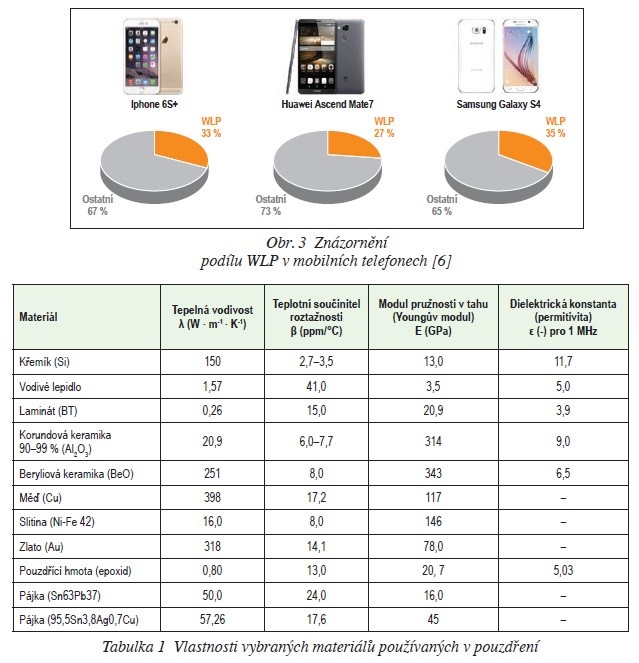

Těchto cílů, především však zlepšení poměru cena/výkon, lze dosáhnout na dvou úrovních pouzdření, a to novými řešeními na samotném waferu (WLP – Wafer Level Packaging) nebo 2,5D/3D uspořádáním pouzdra např. v provedení SIP (System in Package), jehož možnosti jsou znázorněny na obr. 2. Lze si položit otázku, jak se budou vyvíjet moderní způsoby pouzdření a kde nastanou kritická místa v příštích letech?

Mobilní sektor zůstává hlavní oblastí pro aplikaci moderních pouzder na trhu (chytré telefony, tablety). Další oblast aplikací tvoří servery, PC, herní stanice, HDD / USB, WiFi hardware, TV a set top boxy. Pronikání internetu do stále více oblastí života je obecným důvodem pro modernizaci hardwaru, jako jsou chytré domácí spotřebiče, inteligentní města (ve spojení s automobilovým průmyslem) a různá průmyslová zařízení, včetně lékařských aplikací.

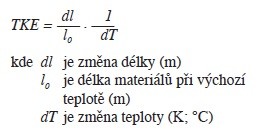

Na obr. 3 je ukázán podíl aplikovaného pouzdření WLP u chytrých mobilních telefonů u třech velkých výrobců. Jak je patrné, téměř jedna třetina polovodičových čipů je v provedení WLP, a lze očekávat, že se tento podíl bude ještě zvyšovat, neboť požadavky na úsporu místa se také nadále zvyšují. Dlouhodobě lze předpokládat další zdokonalování technologie WLP, kde se požadavky budou stupňovat především ze strany internetových aplikací.

Vedle WLP jsou využívány v nemalé míře také holé čipy a čipy v provedení Flip chip, a stále se inovující pouzdra 2,5D / 3D a Si / keramické mezisubstráty.

Problematika pouzdření trochu do detailu

Skutečností je, že v moderních mikroelektronických zařízeních se stále více používají obvody s víceúrovňovou architekturou. Již méně je známo, jaké jevy a procesy se uplatňují uvnitř takových struktur heterogenního charakteru a jaký je jejich vliv na funkci obvodu. Uvnitř pouzdřicí struktury jsou jak organické, tak anorganické materiály, jak kovy, tak izolanty, což znamená, že jednotlivé kompozice mají často značně rozdílné vlastnosti.

Například polymerní materiály mají povrchové napětí a smáčecí vlastnosti jiné než vodivé či anorganické materiály, rovněž teplotní součinitelé roztažnosti jsou většinou značně odlišní. Pro vyloučení destrukčních pochodů a zajištění spolehlivé funkce je nutné kontrolovat celou řadu jevů, z nichž mezi často se vyskytující patří:

- Vyrovnání (Leveling)

- Prohybání, borcení (Sagging)

- Odsmáčení (Dewetting)

- Odlupování vrstev, tvoření dírek/kráterů (Film Retraction/Pinholes)

- Stres (Stress buildup)

- Rozstřikování (Curling)

- Delaminace (Delamination)

- Praskání (Cracking)

Výše uvedené jevy představují pouze vzorek možností, kde povrchové vlastnosti polymerů i dalších materiálů mají zásadní vliv na vlastnosti pouzdření. Tyto jevy je třeba řešit na základě chemie, fyziky a mechaniky povrchů, kde důležitým parametrem je adheze (přilnavost neboli ulpívání materiálů na sobě) a pak také teplotní součinitel roztažnosti TKE, jehož působení se výrazně uplatňuje. Každý materiál má své specifické vlastnosti, jak je patrné z tabulky 1.

Teplotní součinitel roztažnosti TKE vyjadřuje poměrné prodloužení působící mezi dvěma různými materiály. Může být vztažen na délku, plochu nebo objem. Pro výpočet změny délky v závislosti na teplotě platí vztah:

Průběh TKE není obecně v širokém rozsahu teplot lineární, zejména u polymerních materiálů dochází k velké změně hodnoty v oblasti teploty skelného přechodu (Tg), kde materiál přechází z elastického do sklovitého stavu. Například při přímém připojení holých čipů na organické substráty (DPS) má TKE součástky (křemíkový čip) hodnotu 3 ppm/°C a TKE substrátu (FR4) hodnotu 13 ppm/°C.

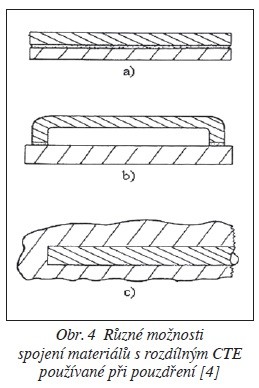

Koeficient tepelné roztažnosti je jedním z klíčových parametrů při návrhu mikroelektronických zařízení, kde jsou spojovány různé materiály. Na obr. 4 jsou uvedeny tři příklady různého spojení materiálů:

a) Vrstvy s odlišným koeficientem roztažnosti spojeny po celé délce (obr. 4a)

- Vrstva IO spojená se substrátovou vrstvou

- Vrstvy skelných vláken ve vrstvě pryskyřice

- Vrstvy vodičů v dielektrických vrstvách

- Substrát připevněný k pouzdru

b) Dvě struktury s různým koeficientem roztažnosti spojené na koncích (obr. 4b)

- Součástky připájeny do děr desky plošných spojů

- Vývody SMT připájené na DPS

- Kovové víčko přivařené ke keramickému pouzdru

- Vývody tranzistoru připájené k substrátu

c) Struktura zapouzdřená v materiálu s odlišným koeficientem roztažnosti (obr. 4c)

- Slitina FeNi pájena v PTH

- Obvody zapouzdřené v ochranném povrchu

- Nosný rám v lisované směsi

- Vývody v pájeném spoji

Je třeba si uvědomit, že pouzdření musí zajistit v přiměřené míře nejen mechanickou ochranu, ale i řadu dalších funkcí, jako jsou ochrana proti vlhkosti, korozi, kontaminaci z prostředí (chlor, draslík, sodík), atmosférické částice (NOX, SO2, emise), ale také elektrická a elektromagnetická kompatibilita čipů, a v neposlední řadě i vedení signálu a odvod tepla.

Vzhledem k tomu, že uvnitř systému se nacházejí různé materiály s různými vlastnostmi, často dochází k mechanickému poškození v důsledku vznikajícího tepla spolu s jevy působícími uvnitř v důsledku odlišných prostředí (např. odstranění škodlivého smykového napětí na kontaktech flip‑čipu mezi čipem a substrátem apod.)

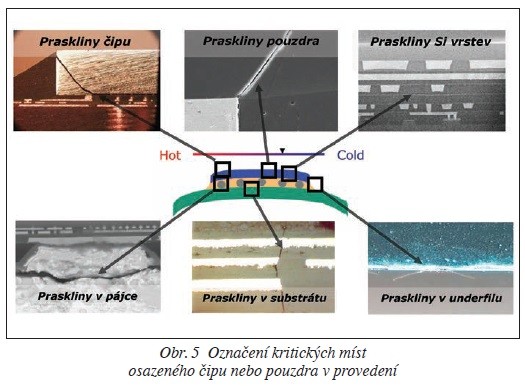

Na obr. 5 je zobrazen konkrétní příklad jednoho z kritických míst v elektronických sestavách, kterým je připojení pouzdra BGA (QFN) nebo polovodičového čipu v provedení Flip-chip na nosný substrát. Základním problémem je zde právě rozdílný teplotní součinitel roztažnosti křemíkového čipu vůči materiálu pouzdra, nosného substrátu či výplňovému materiálu (underfill).

Z obrázku 5 je patrné, že u této jediné součástky je hned šest kritických míst, které mohou být příčinou poruchy a následující nefunkčnosti. Společným jevem, který se zde uplatňuje, je pro všechny typy poruch termomechanické namáhání, které vyvolává pnutí mezi dvěma různými materiály. To způsobuje mechanické poškození, jehož pravděpodobnost se ještě zvyšuje tím více, čím menší jsou rozměry. Řešení těchto problémů není jednoznačnou ani jednostrannou záležitostí, ale závisí na celé řadě dalších, často vzájemně se ovlivňujících souvislostí.

Nejjednodušší forma ochrany čipů před vlivem prostředí je krycí vrstva mikrosystémových součástek nebo celého mikrosystému, kde povlak tvoří především ochranu proti vlivu okolí a škodlivým chemikáliím. Vrstvy mohou být pasivovány přímo na čipu, anebo mohou být pasivovány přímo na waferech (WLP). Zvlášť vhodná vrstva krytí křemíku je dvojitá vrstva oxidu křemičitého a nitridu křemíku. Na křemíkovém čipu rozlišujeme primární pasivaci (před metalizací) a sekundární pasivaci (ochrana, včetně metalizace). Dále se používají organické materiály jako silikonové a fluoro-silikonové gely (tloušťka vrstvy v mm), parylene (odpovídá depozici během CVD procesu) atd. Mikrosystém může být pouzdřen pomocí následujících metod:

- máčení,

- zalévání,

- fluidizace,

- vstřikování,

- lisování (používání kapalin s postupným vytvrzením).

Typické materiály jsou epoxidová pryskyřice, polymerizují čistě a rychle. Anhydridy, aminy nebo fenoly, jsou používány jako tvrdidla. Kyanatan estery mají vyšší skelnou teplotu (190–290 ˚C) a nižší absorpci vody než epoxidová pryskyřice. Uretany se vyznačují výbornou adhezí a vynikající přizpůsobivostí tvaru vrstvy. Akrylátové pryskyřice lze vytvrzovat s použitím UV.

Závěr a role IMAPS

Moderní elektronika nabízí stále více možností pro řešení konstrukce elektronických obvodů a systémů. Existuje nejen řada různých elektronických pouzder, ale i různé možnosti připojení polovodičových i pasivních čipů, různé typy nosných substrátů a také zcela nová řešení jako např. WLP, CSP, SOP, SIP atd. Přitom volba optimálního pouzdra je většinou kompromisem mezi jakostí a cenou. K tomu, aby bylo zvoleno optimální řešení splňující v maximální možné míře obě kritéria, je třeba vhodně zvolit elektrické i technologické řešení, což je náplní problematiky, kterou se zabývá mezinárodní společnost pro mikroelektroniku IMAPS.

Posláním IMAPS je nejen šíření a výměna znalostí a zkušeností z oblasti mikroelektronických montážních technologií, tedy prakticky všeho od čipu až po systém, což je obsahem celé řady konferencí, workshopů a vydávaných tiskovin. Cílem je přitom také tvořit na základě vzájemné důvěry síť odborníků, firem a institucí, jež se zabývají touto problematikou, a přispívat tak k jejich oboustranně prospěšné spolupráci.

Základním článkem je IMAPS se sídlem v USA (http://www.imaps.org/) a s profesionálním vedením, které vydává měsíčně časopis Advancing Microelectronics a organizuje řadu konferencí a workshopů, jejichž vrcholem je každoročně výroční světové sympózium navštívené pravidelně více než 500 účastníky z celého světa. V Evropě je celkem 14 národních sekcí sdruženo v IMAPS Europe (http://www.imapseurope.org), kde každá národní sekce pořádá vlastní konferenci a na závěr roku jsou vyvrcholením alternující evropské konference EMPC (European Microelectronics and Packaging Conference) a ESTC (Electronics System-Integration Conference), pořádané každý rok v jiné zemi. Každé konference je možné se zúčastnit pasivně nebo aktivně, kdy lze prezentovat také vlastní výsledky. V tomto roce jsou tři hlavní konference, a to:

EMPC 2017 21st European Microelectronics and Packaging Conference & Exhibition [2] September 10–13, 2017 Warsaw University of Technology, Poland

- Advanced packaging and interconnects

- Electronics components assembly and PCB solutions

- Materials and processes

- Printed, hybrid and flexible electronics

- Modeling, design test & reliability, Functional systems (actuators, sensors, photovoltaics…)

IMAPS 50th Anniversary Symposium 2017 [1] October 10–12, 2017 Raleigh, USA

- Chip Packaging Interactions (CPI)

- High Performance, Reliability & Security

- Advanced Packaging and Enabling Technologies

- Advanced Packaging & Systém Integration

- Advanced Materials & Processes

3rd IMAPS flash Conference 2017 [3] November 9–10, 2017 Brno University of Technology, Dept.of Microelectronics

- Advanced Packaging, System Integration

- Optoelectronics, Sensors, Actuators, and MEMS

- Integrated Passives, Thick & Thin Film

- Materials and Processes

- Design, Reliability, Security and Environmental protection

Konference české a slovenské sekce IMAPS probíhá tradičně v listopadu na Vysokém učení technickém v Brně (www.imaps.cz) a zahraniční přednášky jsou tlumočeny do českého jazyka. Na konferenci se prezentují zahraniční experti a část je věnována také doktorským přednáškám, jejichž cílem je kromě jiného i navázání spolupráce mezi vysokými školami a firmami.

ODKAZY

[1] www.imaps.org

[3] www.imaps.cz

[4] Szendiuch, I. a kolektiv: Moderní mikroelektronické technologie – základ elektronického hardware, VUT Brno, 2015, ISBN 978-80-214-5293-0

[5] Szendiuch, I.: Pouzdření v mikroelektronice, VUT Brno, 2016, ISBN 978-80-214-5417-0

[6] Yole Développement: Status of the Advanced Packaging Industry report 2015, November 2015