Programovací jazyk ABEL-HDL podobně jako jazyky VHDL, Verilog nebo System C slouží pro popis designu obvodů typů GAL, CPLD a některých malých FPGA obvodů. Jazyk ABEL, který ve svých vývojových prostředích podporují firmy Xilinx a Lattice, je poměrně jednoduchý. Popis designu se odehrává na úrovni low-level (úroveň registrů), podobně asi jako programování v assemblerech pro procesory. Pro srovnání – jazyk VHDL na FPGA platformě by odpovídal jazyku C u procesorů. V následujícím textu si ukážeme strukturu jazyka ABEL, příklady použití a porovnání s jinými HDL jazyky tak, aby vývojář, který jazyk ABEL nikdy nepoužíval, byl po přečtení článku s ním schopen začít ihned pracovat.

Projekt v jazyce ABEL se skládá z jednoho nebo několika modulů. Každý modul obsahuje kompletní logický popis designu nebo jeho části v případě použití několika modulů. Každý modul je sesazen z několika sekcí − MODULE, INTERFACE, TITLE, DECLARATIONS, DEVICE, EQUATIONS, TRUTH_TABLE, STATE_DIAGRAM, TEST_VECTORS, END − které si nyní popíšeme. Dále jazyk ABEL používá několika direktiv (pseudoinstrukcí), které jsou popsány v následující kapitole.

Tyto dvě sekce začínají, resp. ukončují, jednotlivý modul. Za klíčovými slovy MODULE a END by měl následovat ještě jednoslovný název modulu, který smí obsahovat maximálně osm znaků. V jazyce VHDL nemají ekvivalent.

Klíčové slovo INTERFACE má dva významy. Jednak označuje sekci, která popisuje vstupy a výstupy modulu. Pokud se design skládá pouze z jednoho modulu, pak tato sekce není povinná. Pokud se však zdrojový kód programu skládá z několika modulů, pak každý submodul musí obsahovat svoji vlastní sekci INTERFACE. Dále se používá ve funkci příkazu, který připojuje submodul. Tento příkaz se umístí v sekci DECLARATIONS. Na rozdíl od jazyka VHDL jazyk ABEL umožňuje pouze jednu podúroveň submodulů. V jazyce VHDL odpovídá příkazu component. Blíže viz literatura.

Sekci TITLE je možné použít pro název projektu, krátký popis zdrojového kódu apod. Současně se vypisuje v některých výstupních souborech překladačů. Textový řetězec může obsahovat maximálně 324 znaků a může být rozepsán do více řádek.

Sekce umožňuje sdělit překladači jazyka ABEL referenci a typ CPLD obvodu, do kterého je design implementován. Použitím této sekce se návrh stává obvodově závislým, proto nové překladače umožňují její vypuštění. V jazyce VHDL nemá ekvivalent.

První velmi důležitá sekce, ve které se deklarují vstupy/výstupy CPLD obvodu, dále vnitřní signály a módy makrobuněk. Současně se zde zpřístupňují hardwarově vestavěné periférie CPLD obvodů. V jazyce VHDL odpovídá příkazu entity.

Příklad: Vstup, Nulovani pin 7, 10; Nastaveni pin istype ’Reg, Invert‘; Vystup node istype ’Reg_JK, Buffer‘; XLAT_PG(D, E, Q);

Druhá velmi důležitá sekce je prakticky nejdůležitější v celém designu. Provádí se zde popis zapojení pole kombinační logiky AND-OR-INVET pomocí kombinačních logických funkcí rovnicemi. K poli AND-OR-INVET se zde připojují rovněž hardwarově vestavěné periférie CPLD obvodů. Oproti jazyku VHDL jazyk ABEL umožňuje pracovat pouze s logickými úrovněmi log 0 a log 1. Jiné logické úrovně jako měkká nula, tvrdá jednička či vysoká impedance(!) nepodporuje. I když se na první pohled nezdá, tak tato restrikce je svým způsobem výhodou, neboť není nutné různé druhy logických úrovní složitě konvertovat.

Tato třetí důležitá sekce umožňuje zadání kombinační logické funkce tabulkou. Tato kombinační logická funkce se implementuje do pole kombinační logiky (Routing Pool) typu AND-OR-INVET. V jazyce VHDL bychom snad našli příkazy process dále if nebo elsif, jejich použití je vzdáleně ekvivalentní sekci TRUTH_TABLE v jazyce ABEL.

Sekce slouží k verifikaci a ověření funkčnosti designu na simulátoru. Nutno podotknout, že jazyk ABEL mnoho možností ověření funkce designu neumožňuje − lze provést pouze funkční a časovou simulaci, což ve většině případů postačuje. Jazyk ABEL dále neumožňuje provést zapojení vně designu na rozdíl od jazyka VHDL.

Testovacími vektory se obvykle vybudí celý design CPLD obvodu při současné kontrole výstupu obvodu. Časovou prodlevu mezi jednotlivými vektory lze nastavit pouze globálně pro všechny vektory stejně, což je pro designéra poněkud nepohodlné pro nutnost vytvoření poměrně značného množství testovacích vektorů bez chyby.

Vývojová prostředí pro odstranění této nedokonalosti umožňují testování designu vytvořeného v jazyce ABEL pomocí jazyka VHDL a obráceně – design obvodu napsaný v jazycích VHDL nebo Verilog lze testovat pomocí testovacích vektorů jazyka ABEL. Tuto druhou možnost lze využít především v případě, kdy se design napsaný v jazyce ABEL převádí do jazyka VHDL nebo Verilog. Tímto se ověří správnost převedení designu.

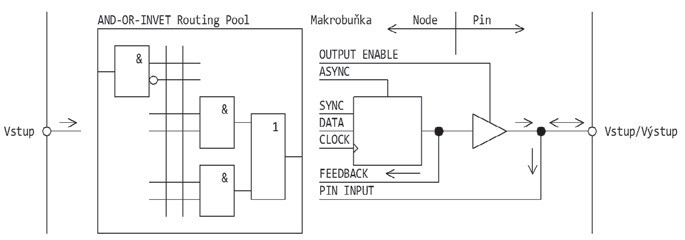

Běžné CPLD obvody se skládají z pole kombinační logiky (Routing Pool) typu AND-OR-INVET a makrobuněk (LMC – Logic MacroCell), které lze naprogramovat jako kombinační nebo jako sekvenční. Při sekvenčním naprogramování lze použít detailního popisu makrobuňky nebo popisu Pin-to-Pin.

Makrobuňku lze naprogramovat jedním typem klopného obvodu z nejširšího množství, které je k dispozici – typu RS, D, JK, T, Latch a D s hradlovanými hodinami. Některé obvody, např. obvody typu GAL, naprogramování všemi typy klopných obvodů neumožňují. O možnosti naprogramování makrobuňky je nutné se dočíst v dokumentaci k příslušnému CPLD obvodu, který zamýšlíme v designu použít.

Blokové schéma makrobuňky je na obr. 1, který vzdáleně připomíná programátorský model CPLD. Názvy signálů jsou na obrázku pouze symbolické. Všeobecně lze říci, že každý klopný obvod obsahuje asynchronní a synchronní řídicí signály. Dále hodinový vstup nebo vstupy, datové vstupy a výstup nebo alespoň výstup zpětné vazby.

V režimu Pin se dále ještě přidává výstupní oddělovač a oboustranně komunikující vstup/výstup na pin CPLD obvodu.

Dále je zakresleno, která část makrobuňky se využije při naprogramování v režimu Node a která část se přidává při naprogramování v režimu Pin.

Makrobuňku lze dále naprogramovat ještě v rozšiřujících módech buffer nebo invert. Mód invert provádí negaci určitých datových nebo řídicích signálů. Mód buffer tuto negaci neprovádí.

Porovnáním manuálů jazyka ABEL firem Lattice Semiconductor a Xilinx bylo zjištěno, že označování funkčně shodných signálů makrobuněk je mezi těmito výrobci ne vždy totožné. Pokud převádíme design CPLD obvodu od jednoho výrobce ke druhému, pak je nutné příslušná označení změnit.

Sekce STATE_DIAGRAM − konstrukce stavového diagramu (automatu) − je jedinou částí jazyka ABEL, kterou bychom mohli zařadit do kategorie „vyššího programovacího jazyka“. Principiálně je velmi podobná, ne-li téměř shodná, s jazykem VHDL. Z tohoto důvodu se jí zde nebudeme věnovat. Podrobnosti v literatuře.

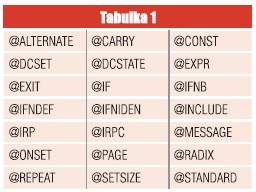

Jedná se v podstatě o pseudoinstrukce pro překladač. Některé direktivy zpřehledňují a zjednodušují zápis jazyka ABEL. Přehled direktiv jazyka ABEL je uveden v tabulce 1.

Vzorový příklad odzkoušený ve vývojovém prostředí ispLEVER Classic ukazuje konstrukci synchronního čítače s asynchronním přednastavením.

Program začíná sekcí MODULE a je ukončen sekcí END. Sekce INTERFACE umožňuje použití tohoto designu v roli submodulu.

V sekci DECLARATIONS jsou zadeklarovány vstupy/výstupy do/z CPLD obvodu a vnitřní signály. Rovněž jsou naprogramovány typy makrobuněk – detailní popis v kombinaci s popisem Pin-to-Pin. Bitové signály jsou sdruženy do vektorů.

MODULE Citac

INTERFACE (Hod, Load, Val2..Val0 -> Q2..Q0);

TITLE ’Tribitovy citac s prednastavenim.‘

DECLARATIONS

// Vstupy do CPLD obvodu

Hod pin;

Load pin;

Val2..Val0 pin;

// Vystupy z CPLD obvodu

Q2..Q0 pin istype ’Reg_D, Buffer‘;

// Vnitrni signaly v CPLD obvodu

Reset2..Reset0 node;

Set2..Set0 node;

// Sdruzeni signalu do vektoru

Val = [Val2..Val0];

Reset = [Reset2..Reset0];

Set = [Set2..Set0];

Q = [Q2..Q0];

EQUATIONS

// Realizace prednastaveni

Reset = !Load & !Val;

Set = !Load & Val;

// Pripojeni klopnych obvodu

Q.CLK = Hod;

Q.AR = Reset;

Q.AP = Set;

TRUTH_TABLE

( Q :> Q )

0 :> 1 ;

1 :> 2 ;

2 :> 3 ;

3 :> 4 ;

4 :> 5 ;

5 :> 6 ;

6 :> 7 ;

7 :> 0 ;

TEST_VECTORS

( [ Load, Val, Hod ] -> Q )

[ .k. , 7 , 0 ] -> .x.;

@REPEAT 8

{ [ 1 , 0 , .u. ] -> .x.; }

END Citac

Všechny předchozí sekce lze považovat pouze za informativní. Teprve sekce EQUATIONS a TRUTH_TABLE popisují vlastní funkci designu (zapojení).

Sekce EQUATIONS provádí popis pomocí kombinačních logických rovnic, a to především asynchronní přednastavení čítače a připojení hodinového signálu.

Sekce TRUTH_TABLE provádí popis zpětné kombinační logiky čítače pomocí pravdivostní tabulky v módu Pin-to-Pin makrobuněk.

Design je otestován pomocí testovacích vektorů sekce TEST_VECTORS, kdy je čítač nejdříve asynchronně přednastaven na hodnotu 7 binárně a potom čítá svých 8 stavů. Pro zjednodušení zápisu bylo využito direktivy @REPEAT.

Programovací jazyk ABEL-HDL je vhodný pro design CPLD obvodů, které obsahují desítky až stovky makrobuněk, jejichž programování se provádí na low-level úrovni. Výhody přináší jeho jednoduchost – seznámení se s ním nezabere designérovi více než den. Tuto skutečnost ocení především studenti, kteří jeho studium mohou mít jako předstupeň k poznání velmi komplikovaných jazyků VHDL nebo Verilog. Jazyk ABEL dále umožňuje velmi efektivně zaplnit hradlové pole k jeho hranici technických možností. Naprosto shodný design napsaný v jazyce VHDL může požadovat použití většího CPLD obvodu, a tím zvýšit výrobní náklady. Zkuste implementovat např. 32bitový čítač do obvodu Lattice ispLSI 2032 pomocí jazyka VHDL. Doufám, že někdo tuto pomyslně hozenou rukavici zvedne. I když se jedná o jazyk velmi starý – poslední revize je z roku 2007 – a nedochází již k jeho rozvoji, lze se přesto domnívat, že v oblasti hradlových polí CPLD bude ještě dlouho používán.

[1] ABEL-HDL Reference Manual, Lattice Semiconductor Corporation

[2] ABEL-HDL Design Manual, Lattice Semiconductor Corporation

[3] ABEL Reference Guide, Xilinx Inc.

[4] www.xilinx.com/itp/xilinx10/help/iseguide/mergedProjects/abelref/abelref.htm