V high-speed obvodech desky je napájecí integrita (integrita napájení desky) důležitým námětem k diskuzi hned vedle signálové integrity. Cílem napájecí integrity je dosažení přenosu čistého high-speed signálu zajištěním dobrého napájení součástek, které jsou zdrojem signálů. Dobré napájení musí splňovat dva požadavky: 1) dodržení požadavků na DC napájení a 2) snížení napěťového šumu napájení způsobené spínáním AC proudu. Tento článek probere proces simulace napájecí integrity při použití CST PCB STUDIO® (CST PCBS). Zkušební deska má 6 vrstev s jejich typickým rozložením S-P-S-S-G-S, kde S = signál, P = napájecí vrstva (plane) a G = zemnicí vrstva (ground).

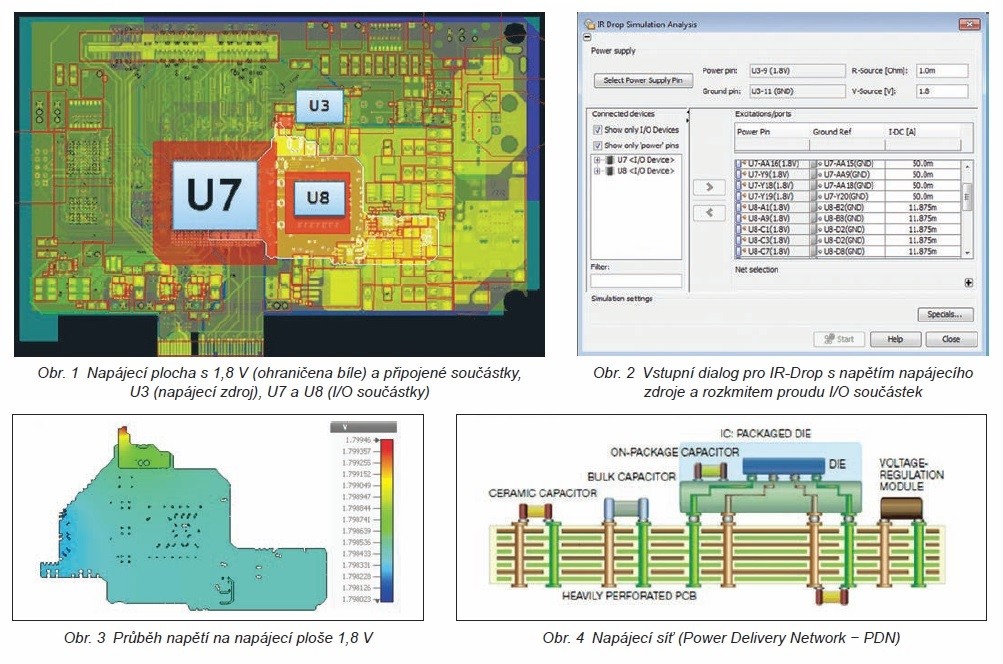

DC napájecí integrita, také známá jako IR-Drop, je statická napájecí integrita, která zahrnuje zdroj potřebného napětí a proud pro každý zdroj signálu. Simulace IR-Drop v CST PCBS je založena na statické rovnici pro metodu PEEC (Partial Element Equivalent Circuit), která vyžaduje pouze malý výpočetní výkon, protože generovaný ekvivalent sítě je čistě odporový. IR-Drop simulace je typicky provedena na začátku návrhu, protože může být provedena rychle i pro velké desky plošných spojů. V tomto článku má napájecí plocha desky napětí 1,8 V a jsou na ni připojeny dvě I/O součástky: U7 (grafický procesor) a U8 (DDR2 RAM). Aby bylo možné získat správný pokles DC napětí přes celou napájecí plochu, je doporučeno sledovat správnou elektrickou specifikaci každé součástky, zejména: 1) výstupní napětí DC-DC konvertoru jako zdroje napětí a 2) celkovou spotřebu proudu high-speed I/O součástky připojené k napájecí vrstvě. V tomto případě máme 16 vývodů součástky U8, které spotřebují 190 mA, a 7 vývodů od U7 s celkovou spotřebou 350 mA. Obrázek 1 ukazuje napájecí plochu s 1,8 V a s připojenými součástkami, zatímco obrázek 2 ukazuje informaci pro nastavení IR-Drop simulace.

Rozdělení napětí na napájecí ploše 1,8 V je znázorněno na obr. 3. Protože maximální dovolené kolísání napětí je ±0,1 V, je celkový povolený rozkmit napětí 0,2 V. Při typickém rozkmitu DC napětí kolem 20 %, obě I/O součástky připojené na napájecí plochu 1,8 V pořád ještě splňují kladené požadavky.

Simulace AC napájecí integrity vyžaduje více výpočetního výkonu než u DC, protože nyní zahrnuje vliv rozmístění součástek a vliv PDN (Power Delivery Network) součástek, jako jsou kondenzátory a VRM. V úvahu se bere hustota proudu u via otvorů a v napájecí ploše, zejména oblast VRM blízko rychle spínajícího výstupu I/O součástky. Protože velký proud představuje vysokou impedanci a indukčnost se zvyšuje s kmitočtem, cílem simulace AC napájecí integrity je minimalizovat PDN impedanci, což pomůže vyhnutí se kolísání napětí při spínání. Minimalizování PDN impedance může být snadno dosaženo kalkulací konečné impedance podle rovnice:

Pro napětí 1,8 V s povolenou odchylkou 0,2 V a 20% DC odchylkou zbývá 80 % pro AC rozsah napětí, což je 0,16 V AC napěťového šumu. Za předpokladu, že střídavý proud je 540 mA, je cílová impedance 0,29 Ω napájecí plochy definovaná jako cíl pro PDN impedanci, aby se zajistilo maximální povolené kolísání napětí při daných podmínkách spínání.

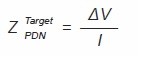

PDN impedance je naopak definovaná vyhodnocením každého vývodu, který je zdrojem signálu. Obr. 5 ukazuje PDN impedanci holé desky (zelená křivka) při zaměření se na vývod A1 součástky U8. Ta je typicky ve tvaru V křivky, když začne jako kapacitní při nízkých kmitočtech a změní se na induktivní při vysokých kmitočtech. Druhý vrchol kolem 683 MHz ukazuje rezonanci napájecí plochy. Aby se PDN impedance minimalizovala, byly přidány mezi napájecí a GND plochu blokovací kondenzátory. Kondenzátory přidají desce parazitní kapacitu a tak posunou rezonance. Červená křivka na obr. 5 představuje osazenou desku s několika přidanými kondenzátory. Předchozí rezonance při 683 MHz je nyní posunuta dolů k nižším kmitočtům. Protože kondenzátor při vysokých kmitočtech představuje zkrat, PDN impedance se při vyšších kmitočtech nezmění a zvýšení kapacity blokovacích kondenzátorů se projeví jenom jako malé vylepšení. Z toho vyplývá, že zlepšení PDN impedance při vysokých kmitočtech je náročnější úlohou, která vyžaduje více kroků – analýzu impedance napájecí plochy, zlepšení rozmístění součástek na desce a výběr blokovacích kondenzátorů s nízkou parazitní indukčností.

Prostorový plot impedance pro holou a osazenou desku je ukázán na obr. 6. Impedance napájecí plochy holé desky na obr. 6a ukazuje dodatečnou vyšší impedanci jako impedanci od napájecího vývodu U8 A1. Ta je hlavně způsobená rezonancí napájecí plochy, která může být odsunuta pryč použitím blokovacího kondenzátoru v oblasti rezonance, jak je ukázáno na obr. 6b.

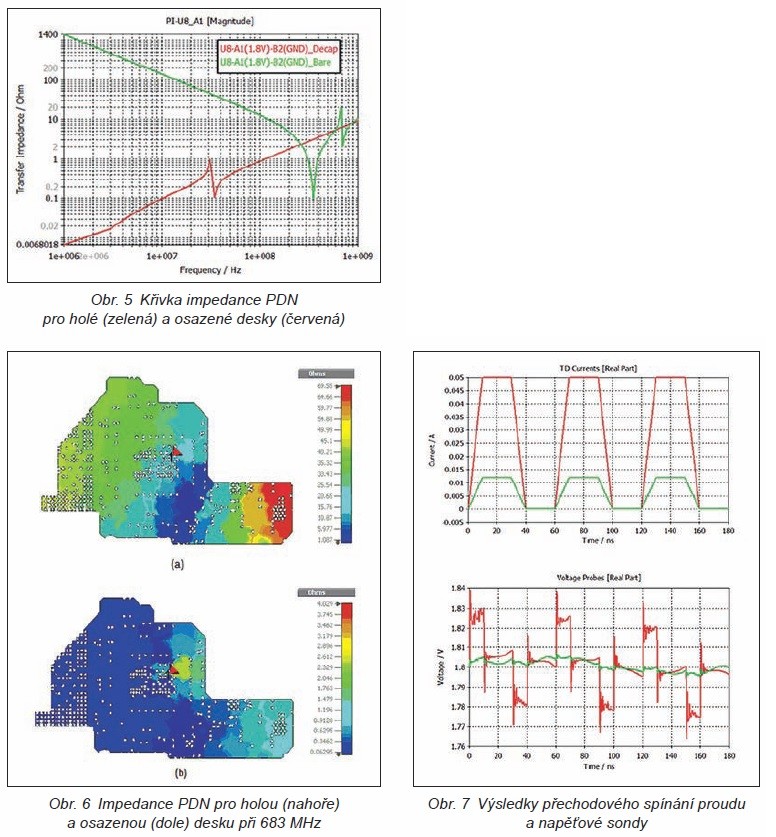

Jako konečné ověření analýzy napájecí integrity bude ukázáno přechodové chování napětí napájecího zdroje. Přechodový proud bude pro I/O součástku potřebný, aby mohla vyslat spínaný signál. Každý z 16 vývodů U8 a 7 vývodů U7 je zapojen na odpovídající IBIS vývod napájecího zdroje a „1010“bitová sekvence pro modelování spínání přechodového proudu je dodána na každý ovládací vývod IBIS. Přídavné napěťové sondy jsou umístěny na každý spoj napájecího zdroje k monitorování přechodového napětí během IBIS spínání. Výsledky z napěťových sond jsou vidět na obr. 7, kde jsou kvůli lepší vizualizaci ukázány pouze výsledky od dvou vývodů U7 a U8.

Obr. 7 ilustruje výsledky přechodové simulace od napěťových sond. Pro lepší porozumění je také plotován výsledek přechodového spínání proudu, který lze vidět v horní části obr. 7. Červená křivka představuje výsledek od U7, zatímco zelená křivka je výsledek od U8. Z nich je zřejmé, že pokaždé, když došlo ke spínání proudu, došlo ke kolísání napájecího napětí na součástce. S vyšším spínaným proudem a rychlejším spínáním součástky roste napěťový šum, což vyžaduje další snížení PDN impedance.

V tomto článku je prezentován postup při analýze napájecí integrity high-speed desek plošných spojů. Analýza je provedena pro DC i AC. Jedním z hlavních cílů je optimalizování PDN impedance v kmitočtové doméně, aby se minimalizoval šum napětí napájecího zdroje. Přechodová simulace zajišťuje užitečnou ukázku toho, jak je důležité minimalizovat PDN impedanci kvůli zajištění nízkého napěťového šumu.