Při návrhu aplikací se smíšenými signály je vždy nejdůležitějším krokem volba vhodné architektury analogově-digitálního převodníku. V následujícím článku se zaměříme na srovnání vlastností převodníků s postupnou aproximací (SAR) a převodníků s delta-sigma (ΔΣ) topologií.

Cílem následujícího článku je pomoci s výběrem té nejlepší architektury pro vaši konkrétní aplikaci. Zaměříme se na srovnání klíčových vlastností obou uvedených typů. Především tedy z hlediska vzorkování měřeného signálu, vlastností zrcadlových filtrů i schopnosti zpracování vícekanálových signálů.

Mezi oběma architekturami je možné vidět velké rozdíly již v jejich principu získávání vzorků vstupního signálu. Obvod SAR provádí převod analogového signálu na digitální v přesně daný čas A. Přesně v tento okamžik je vždy zahájena konverze. Naproti tomu ΔΣ převodník poskytuje průměrné hodnoty, zachycené v časovém intervalu tA. Výstupem převodníku této architektury je tak průměrná hodnota napětí, získaná několikerým převzorkováním vstupního signálu. To však zároveň znamená, že u tohoto typu obvodu není možné spočítat reálnou analogovou hodnotu pro určitý časový okamžik. Vzhledem k tomu zde rovněž není vyžadována ani žádná spouštěcí událost – trigger. Z toho jednoznačně vyplývá, že ΔΣ převodníky jsou vhodnější pro kontinuální měření a pravidelné poskytování hodnot měřeného signálu.

Na řadu algoritmů číslicového zpracování signálu, má zásadní vliv především znalost rychlosti přenosu dat, označovaná jako fDR. Zásadní vliv, například na možnost použití rychlé Fourierovy transformace (FFT), může mít i správné načasování dat podle fDR. V tomto případě však nesmí být fDR zaměňována za vzorkovací frekvenci fA. Vzorkovací frekvence fA totiž určuje frekvenci, s níž je vzorkován analogový signál. Na rozdíl od fDR, která označuje frekvenci, při níž jsou na výstup obvodu odesílána již zpracovaná digitální data.

V případě ΔΣ konvertoru je přitom fDR přímo úměrná fA. Poměr těchto dvou frekvencí je označován jako hodnota převzorkování – R. Změna v fA zde tedy přímo ovlivňuje změnu fDR. Avšak existují i ΔΣ převodníky – jako je například obvod ADS1115[1], v němž je jako zdroj hodin využit pouze vnitřní oscilátor, kmitající s přesností kolem ±10 %. V takových případech není hodnota fA (a tedy ani fDR) zcela přesně známa, což však v řadyě aplikací nevadí. O tom se však zmíníme ještě později.

V kontrastu s tím, jsou digitální data v převodnících SAR generována pro každý jednotlivý analogový vzorek. Frekvence fDR je zde tedy totožná s fA. Tato frekvence je v podobných obvodech přiváděna buď na vyhrazený, k tomu určený pin, nebo volitelně dodávána pomocí synchronizace na pinu slave select/frame sync. To platí především v SAR se sériovým rozhraním.

Jak všichni velice dobře víme, každý A/D převodník vyžaduje omezení vstupního signálu do určité frekvence. To je z důvodu dosažení souladu s Nyquist-Shannonovým teorémem vzorkování. Ten říká, že nejvyšší frekvence vstupního signálu fSig_max, nesmí překročit polovinu fA. Analogový dolnofrekvenční filtr, rovněž nazývaný jako zrcadlový (antialiasing) filtr (AAF), je zodpovědný za požadované omezení frekvenčního pásma. Pokud chcete co možná neefektivněji využít šířky pásma použitého převodníku, je třeba využít ideální dolní propusti se zlomem na fA/2. Nicméně v praxi je toto samozřejmě nerealizovatelný problém. V praxi je možné pouze jisté přiblížení ideálnímu filtru a to s použitím filtru vysokého řádu. Jedinou výhodou je zde skutečnost, že frekvence signálů, nacházejících se pod rozlišením A/D převodníku, zde nepředstavuje žádné problémy.

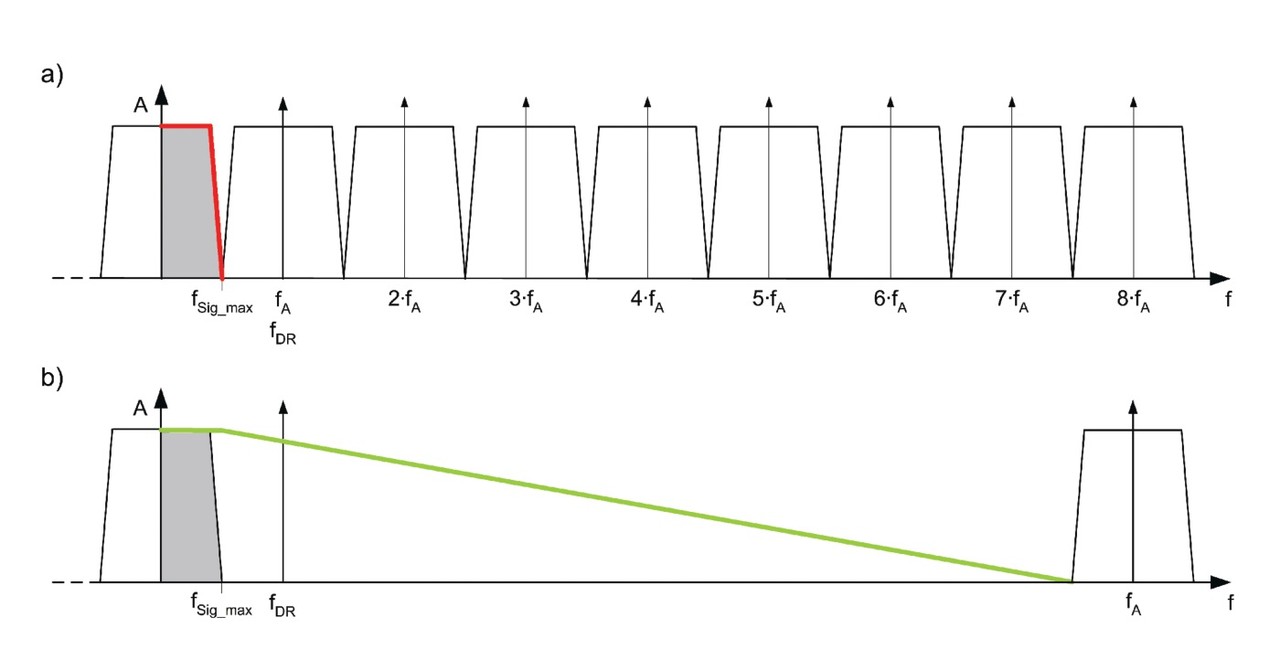

Obr. 1. Frekvenční spektrum digitálního signálu

Obrázek 1a ukazuje frekvenční spektrum digitálního signálu, určeného pro SAR převodník. Zároveň je zde zvýrazněno i omezení pásma analogového vstupního signálu na fa/2, s ohledem na vzorkovací teorém.

U ΔΣ převodníku je fA mnohem vyšší než fDR a to kvůli jeho nadměrnému vzorkování. To tedy znamená, že fA je na rozdíl od SAR přesunuta na vyšší frekvenci (obr. 1b). Pro příklad, dejme tomu, že R = 8. Ačkoli typické hodnoty R jsou i kolem 128 a více. I přesto však použitelná šířka pásma analogového vstupu zůstává stejná. Návrhářům je tak k dispozici mnohem více frekvenčního prostoru pro zrcadlový filtr, což zajistí snazší dosažení požadovaného útlumu. Obecně řečeno, u ΔΣ převodníků bohatě vystačíme s filtrem prvního či druhého řádu. V případě ΔΣ převodníku by navíc zrcadlový filtr měl být navržen v souvislosti s integrovaným digitálním filtrem. Ten je poté zodpovědný za úplné omezení frekvenčního pásma.

Další výhodou ΔΣ převodníků je, že vnitřním filtrem je přímo ovlivněna fDR. To nabízí celou řadu výhod, jako je především možnost nastavení fDR ve vztahu k aktuálnímu vstupnímu signálu. Navíc přímo v reálném čase (změnou fA a/nebo R), vedoucím ke snížení zbytečného objemu dat. Převodník typu SAR tuto možnost nenabízí. V jeho případě by snížení fA bylo v přímém rozporu s Nyquist-Shannonovým teorém vzorkování, protože externí zrcadlový filtr obvykle není možné měnit.

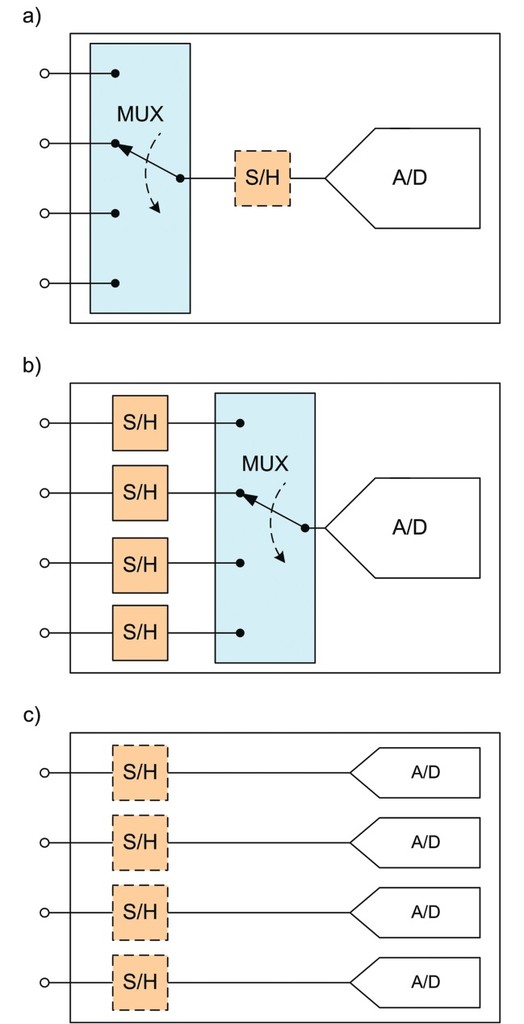

V aplikacích, které vyžadují měření více signálů, se obvykle využívají A/D převodníky s integrovaným vstupním multiplexerem (obr. 2a). Integrovaný multiplexer přepíná různé analogové kanály v určeném pořadí a signály z nich přivádí na tzv. sample-and-hold (S/H) obvod (v případě SAR převodníku) nebo přímo na A/D jednotku (v případě ΔΣ převodníku). Více o vlastní architektuře obvodů je možné nalézt například v technických listech obvodů ΔΣ: ADS1258[2] a SAR: ADS7953[3]. Základní fDR převodníku tak musí být sdílena mezi jednotlivým i kanály. Je však třeba počítat i se skoky v napětí, vznikajících při přepínání jednotlivých kanálů. Z tohoto důvodu musí být zachováno vždy určité množství času, určeného pro ustálení nového signálu na vstupu konvertoru (v důsledku toho je reálná fDR dokonce snížena).

Obr. 2. Možná provedení integrovaných vícekanálových ADC

Jakmile dojde k ustálení signálu, je SAR převodník připraven k použití a může být spuštěna nová konverze, která okamžitě dodá platný výsledek. Zpoždění pro ustálení, které se definuje jako počet cyklů převodu, které jež je třeba ignorovat, než na výstupu převodníku získáme platné informace, je tedy rovné nule.

Výpočet zpoždění v případě ΔΣ převodníku je poněkud složitější. Zde je třeba rozlišovat obvody dle typu integrovaného digitálního filtru. Pokud má být využita celá šířka propustného pásma, tedy až do hodnoty fDR/2, používá se filtr typu FIR (finite impulse response). Vzhledem k jeho vysokým nárokům na frekvenční odezvu a související délku filtru, nejsou není ničím neobvyklým zpoždění i více než 50 konverzních cyklů.

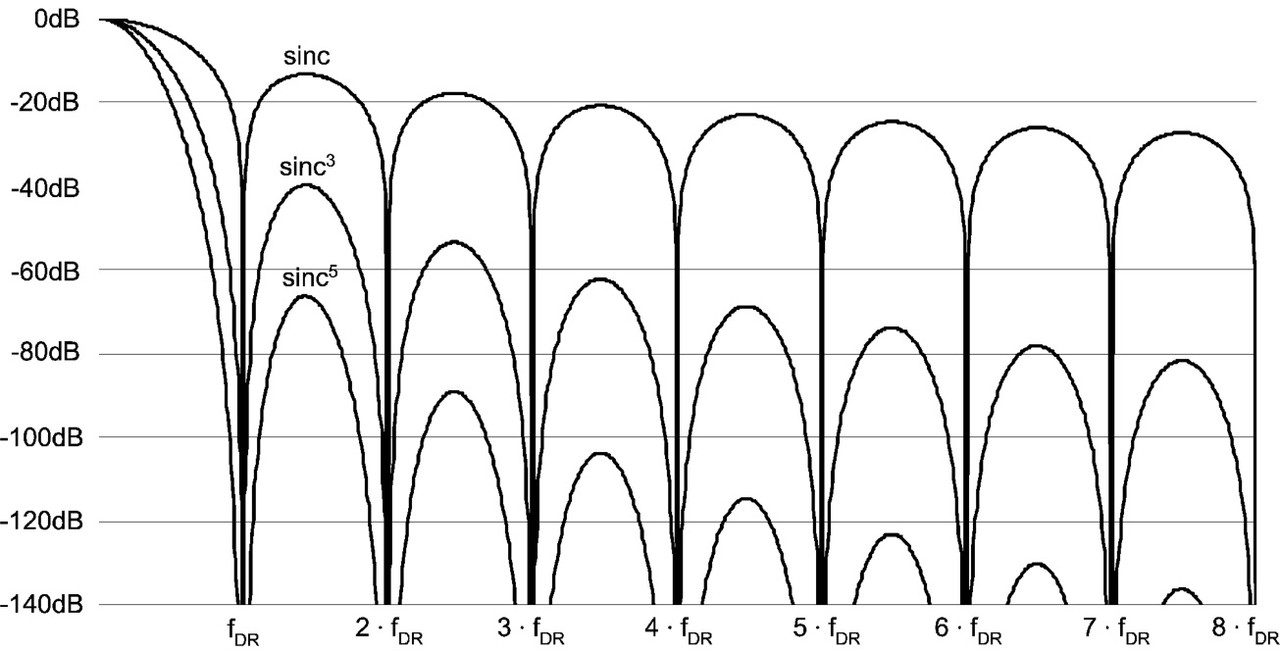

Možnou alternativou je takzvaný sinc filtr. Tento filtr se velmi snadno implementuje a může být libovolně kaskádovitě násoben. Počet kaskád označuje řád filtru. Obrázek 3 zachycuje frekvenční odezvu filtru prvního (sinc), třetího (sinc3) a pátého (sinc5) řádu (kaskády). Obdobně z Z pořadí filtru vyplývá obdobně i jeho zpoždění. Z frekvenční charakteristiky je patrné, že tento typ filtru nemá žádný útlum pro stejnosměrné (DC) signály (tedy f = 0 Hz). V důsledku toho jsou sinc filtry nejvhodnější pro vstupní signály, které se v časové oblasti mění jen pomalu. Vzhledem k tomu je zde zájem především o absolutní hodnotu. V podstatě není třeba znát ani přesnou rychlost přenosu dat, čímž se otevírá cesta pro použití integrovaného zdroje hodinového signálu. Podobně je řešen například již zmíněný obvod ADS1115. Mezi cílové aplikace takového řešení, je možné zahrnout například měření teploty či sledování stavu baterie. Jedním z důsledků, plynoucím z této souvislosti je, že šum je pro ΔΣ převodníky se sinc filtrem obvykle definován jako absolutní hodnota. Naproti tomu u ΔΣ převodníků s FIR filtrem je a definován jako relativní hodnota, ve vztahu k signálu – tedy SNR. Vzhledem k malému zpoždění, které je třeba uvažovat při každé změně kanálu u ΔΣ převodníky s integrovaným multiplexerem a sinc filtrem, má samozřejmě i toto vliv na omezení šířky pásma signálu. Nicméně je tato hodnota stále vzdálena zpožděním, vznikajících na SAR převodnících.

Obr. 3. Frekvenční odezva sinc filtrů

V některých případech je však konfigurace z obr. 2a nedostatečná k tomu, aby zajistila dostatek informací z několika souběžných signálů. Takzvaná současná aproximace, tedy konverze několika signálů zachycených v jediný okamžik, je důležitá například v aplikacích řízení motorů. Zde může vznikat nesourodost jednotlivých dat, právě v důsledku přepínání S/H fází a čekání na ustálení napětí. Možným řešením v SAR převodníku je zařazení multiplexeru až za fázi S/H (obr. 2b). V tomto případě jsou hodnoty všech analogových signálů načteny v jeden okamžik. Následně jsou zmrazeny a postupně převedeny na digitální hodnotu. Tímto řešením je možné zajistit současnou konverzi více analogových kanálů s použitím jediného A/D převodníku, avšak pouze v případě SAR. ΔΣ převodníky neobsahují obvodu S/H.

Nejjednodušším, i když ne zrovna nejlevnějším řešením, je použití samostatného převodníku pro každý analogový signál. V takovém případě již multiplexer není zapotřebí (obr. 2c). Toto řešení je ideální především v aplikacích, ve kterých je třeba zpracovat hned několik širokopásmových signálů zároveň. Společnost Texas Instruments nabízí čipy, které v jediném pouzdře integrují několik převodníků. Například pro ΔΣ je to obvod ADS1278[4] a pro SAR je to ADS8556[5]. Pro každý měřený kanál je tak k dispozici plná šířka pásma a samozřejmostí je možnost spouštění převodu všech kanálů současně.

Jak je vidět, mezi používanými architekturami A/D převodníků existují značné rozdíly. Zatímco například SAR převodník nabízí výhodu v možnosti konverze v přesně daný časový okamžik, převodník ΔΣ vyniká především v nízkých nárocích na vstupní filtr. Další klíčový rozdíl spočívá v hodnotě poměru signál/šum. Díky postupné integraci během převodu ΔΣ obvodu, jsou jím do značné míry zcela ignorovány krátké poruchy. V důsledku toho může ΔΣ převodník zajistit až 120 dB SNR, kdy současné SAR převodníky dosahují svého limitu zhruba na 100 dB SNR.

Jsou to však právě tyto hlavní rozdíly, které mohou vývojářům mohou urychlit rozhodování a volbu vhodného typu převodníku. Jakmile dojde k určení vhodné architektury, je možné využít například nástroje ADC selection wheel pro urychlení výběru vhodného obvodu z široké řady dostupných variant A/D převodníků. Jakmile se rozhodnete, objednejte si vzorky obvodů ještě dnes[6]!