V prvním díle časopisu jsem sliboval, že se hradlovým polím vyhneme. Ale protože jsem sám byl nucen je ve své jedné konstrukci použít, tak se zkusím o své zkušenosti podělit. Moje zkušenosti jsou zde popsány z pohledu člověka, který s nimi začíná. Omlouvám se proto zkušeným návrhářům těchto obvodů za mé případné nepřesnosti. Nebudu se zde zabývat rozdíly mezi typy hradlových polí, ani odlišnostmi mezi výrobci. Ukážeme si práci s hradlovým polem LFE2-20E od firmy Lattice. Tento typ jsem si pro pokusy vybral z prostého důvodu – český dodavatel je měl skladem, stál cca 500 Kč a měl snadno použitelné pouzdro PQFP-208. Vytvořil jsem si tedy autorouterem dvoustrannou desku, na kterou jsem připájel hradlové pole a několik dalších součástek. Tento obvod je dostatečně velký na to, aby se mohl naprogramovat od invertoru až po třeba několik 32bitových procesorů. Popíšeme si, co je potřeba pro počáteční pokus.

Na to si myslím nelze úplně přesně odpovědět. Sám jsem byl ve svých konstrukcích mnohokrát na vážkách. Mám některou funkci naprogramovat do procesoru nebo do hradlového pole? Při pohledu na některé konstrukce se však nestačím divit. Viděl jsem řadič servomotoru včetně pomalé regulační smyčky naprogramovaný v hradlovém poli. Tuto práci by snadno zastal procesor v ceně mnohem menší, přičemž by odpadla složitá úprava potřebné funkce. Na druhou stranu jsem viděl konstrukci, kde velký počet vstupů i výstupů byl realizován pomocí TTL obvodů. Sběrnice se potom po plošném spoji „kroutila” všemi směry. Jelikož tato deska pracovala na dost vysoké frekvenci, bylo potřeba provést komplikované přizpůsobení spojů. Až se tomu návrhu divím, protože pokud by se použilo hradlové pole, tak tyto problémy odpadnou.

Jednou možností, kdy lze s výhodou použít hradlové pole, jsou úlohy, které lze rozdělit na několik paralelně zpracovávaných částí.

Hradlové pole obsahuje především velké množství buněk, kde každá buňka obsahuje logický obvod pro realizaci základních funkcí typu NAND, NOR, AND a registr. Hradlové pole obsahuje také několik PLL jednotek, které slouží pro vytváření pracovní frekvence z kmitočtu externího oscilátoru. Pro vnitřní práci obvodu lze tedy odvodit jakýkoliv kmitočet. Důležitou součástí hradlového pole je paměť SRAM, rozdělená do několika bloků. Tuto paměť lze konfigurovat do funkce dual-portové paměti nebo paměti FIFO. Tuto možnost lze využít například pro rychlou komunikaci mezi procesory.

Další hlavní části hradlového pole jsou obvody vstupu a výstupu, kde jsou jednotlivé piny hradlového pole seskupeny do několika skupin. Každá skupina má svůj vlastní pin pro připojení napájecího napětí a lze ji naprogramovat různě, např. TTL s úrovněmi 3,3 V, popř. jako MOS2.5 a nebo jako např. LVDS. Z toho vyplývá, že do hradlového pole lze přivést některá data jako LVDS signály a na druhé straně třeba budit tranzistory přes TTL výstupy. U každé skupiny lze také naprogramovat terminaci vývodu a proud vývodu tvořící strmost hran. Samozřejmě každý vývod může být naprogramován jako vstupní, výstupní nebo třeba obousměrný.

Náš popisovaný obvod obsahuje také DSP bloky, které lze použít např. pro realizaci číslicových filtrů (násobičky) a bloky pro realizaci řadiče DDR pamětí. Důležitou informací je rychlost. Můžeme říci, že vnitřní hradla jsou asi 10× rychlejší než běžně dostupné obvody TTL řady pro napájecí napětí 3,3 V. Pokud tedy naprogramujeme 16bitovou sčítačku, tak ta dokáže pracovat asi na 600 MHz, přičemž obvod vnitřně pracuje s napájecím napětím 1,2 V.

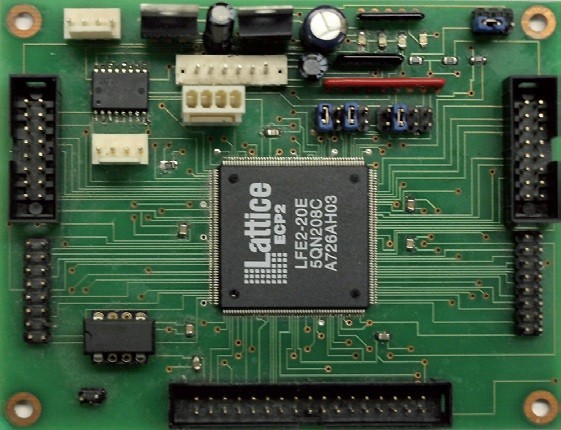

Kupodivu mnoho ne. Vše je vidět na následujícím obrázku pokusné desky. Deska je dvouvrstvá a obsahuje vlastní hradlové pole, krystalový oscilátor a sériovou paměť konfigurace. Tím se ale hradlová pole liší od sebe. Některá paměť obsahují a některá ne, takže potřebují externí paměť. Pole si tedy po připojení napájecího napětí vyčte po SPI z externí paměti konfiguraci a vnitřní propojení buněk. Dále jsou na desce dva lineární stabilizátory. Jeden vytváří napájecí napětí 1,2 V pro vlastní pole, druhý 3,3 V je použit pro napájení vstupně výstupních obvodů. Ke čtyřem pinům jsou připojeny LED diody. Jako první jsem naprogramoval 24bitovou děličku kmitočtu z oscilátoru a na připojených LED bylo vidět, že funguje. Na desce je také několik nezbytných blokovacích kondenzátorů. Všechny zbývající piny mám vyvedeny na lišty okolo obvodu. Programování SPI paměti (zde typ 25P16) provádím pomocí programátoru PRESTO.

Obr. 1 Pokusná deska s hradlovým polem

Podíváme se na to trošku s nadhledem. Máme kontaktní pole o velikosti fotbalového hřiště, vypájeli jsme všechny integrované obvody z několika starých počítačů EC-1045 a máme mnohakilometrovou cívku měděných drátů. A teď to potřebujeme propojit. Potřebujeme to ale provést pomocí počítače na destičce 10×10 cm. Dobrou zprávou je skutečnost, že od výrobce součástky lze z internetu stáhnout zdarma vývojové prostředí. Každý výrobce má svůj systém a je zde vidět konkurenční prostředí. Vývojové prostředky jsou rozsáhlé nástroje, které po instalaci zaberou i několik GB. Tím, že je vývojové prostředí zdarma, snaží se výrobci přilákat konstruktéry k používání jejich obvodů. Jelikož jsou tyto nástroje zdarma, jsou většinou trochu omezeny, ani ne velikostí návrhu, ale možností simulace. Je potřeba si uvědomit, že dnes existují obrovská hradlová pole, u kterých simulace a analýza trvá velmi dlouho. Pro tyto simulace jsou dodávány speciální moduly, které využívají více jader procesoru. V běžné praxi se nás však toto omezení nedotkne. Pro naše hradlové pole použijeme návrhový systém Lattice Diamond, který lze zdarma stáhnout z webu výrobce.

Z mého pohledu jsou 2 možnosti. Jako první a pro začátky i snadnější se mi jeví nakreslení elektrického schématu.

Z knihoven vybereme na plochu součástky typu hradlo, vstupní pin, výstupní pin, registr atd. Součástí návrhového systému je také modul tzv. IpExpress, který umí vygenerovat a přidat do knihovny součástky jako 16bitovou děličku, 32bitový registr, 8 kB SRAM a další typy. Součástky propojíme, pojmenujeme spoje a popřípadě spoje označíme jako vstup či výstup. Druhou možností pro popis je VHDL jazyk, jehož použití je již nezbytné pro složitější návrhy. Nakreslení schématu pro velké a složitě zapojené hradlové pole je prakticky nerealizovatelné. Samozřejmě lze obě možnosti zkombinovat.

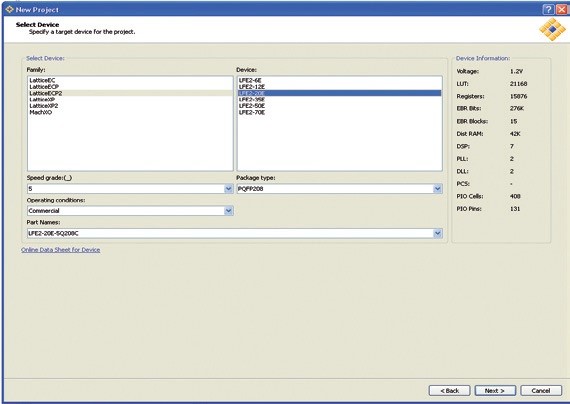

Samozřejmě. Ukážeme si postup pro propojení několika hradel a to od založení projektu až po vytvoření souboru pro programátor. Nebudeme si však zobrazovat úplně všechna okna, ale jenom ta, u kterých by mohly nastat nejasnosti. Nejdříve založíme projekt pomocí interního wizardu. Zadáme adresář a jméno projektu a nepřidáváme další zdroje. Tak se dostaneme k dialogu pro výběr hradlového pole (obr. 2).

Obr. 2 Výběr hradlového pole

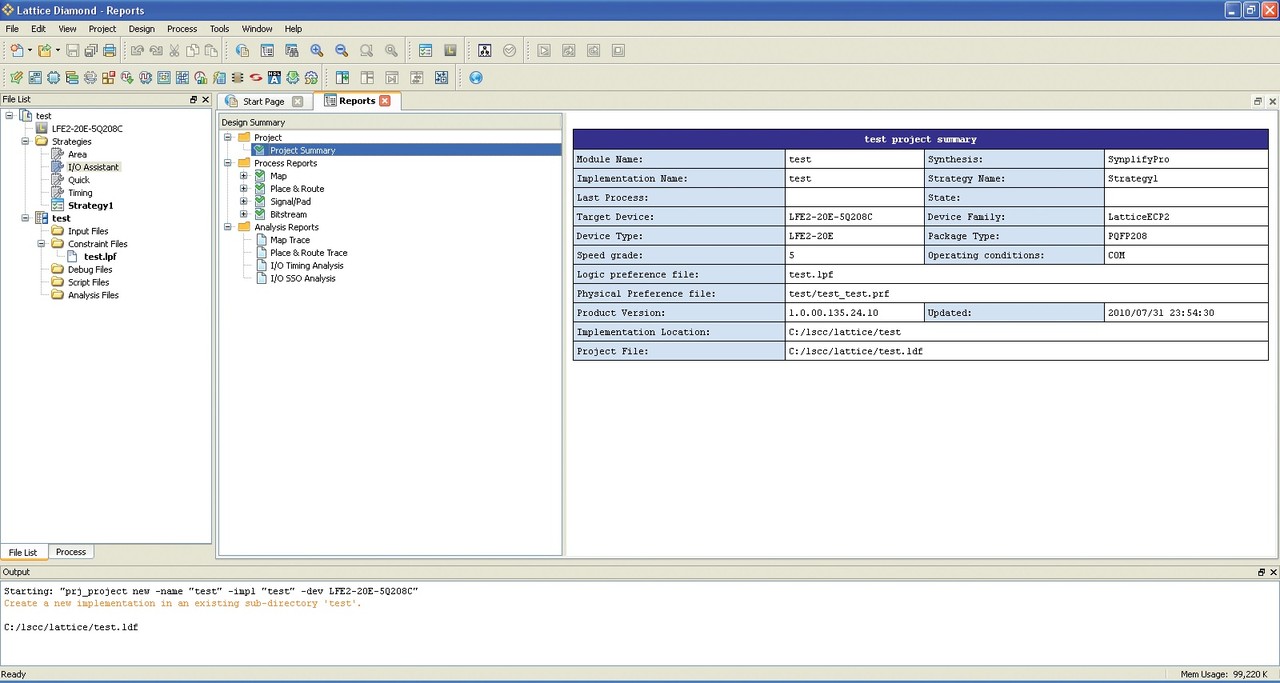

Na následujícím obrázku (obr. 3) je zobrazeno okno, které bychom měli v návrhovém systému vidět také.

Obr. 3 Hlavní okno programu po výběru hradlového pole

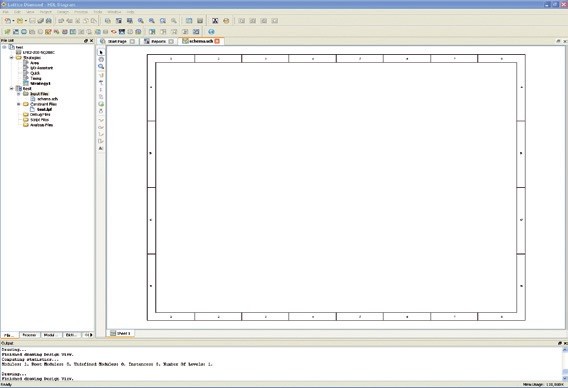

V dalším kroku přidáme zdroj dat, kterým je soubor schema.sch. To provedeme vybráním Input File v levé části okna, dále Add a New file a vybereme soubor schématu. Tím se dostaneme k oknu pro kreslení schématu tak, jak je vidět na obrázku obr. 4.

Obr. 4 Konfigurace pro kreslení schématu

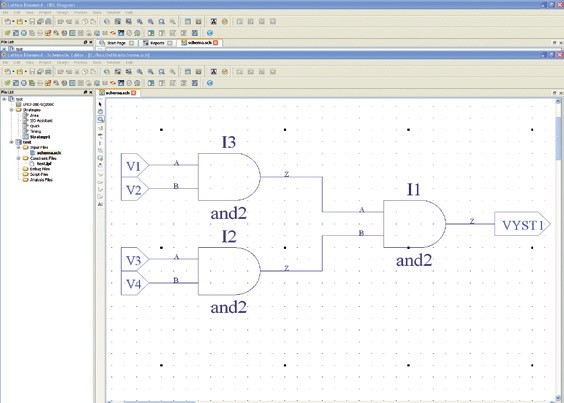

Nyní na kreslicí plochu přidáme 3 hradla, propojíme je a spoje pojmenujeme. Následně spoje označíme jako vstupní a výstupní. Vše provedeme pomocí ikon vedle schématu. Měli bychom tedy mít zapojení tak, jak je vidět na obr. 5.

Obr. 5 Kreslení schéma pro hradlové pole

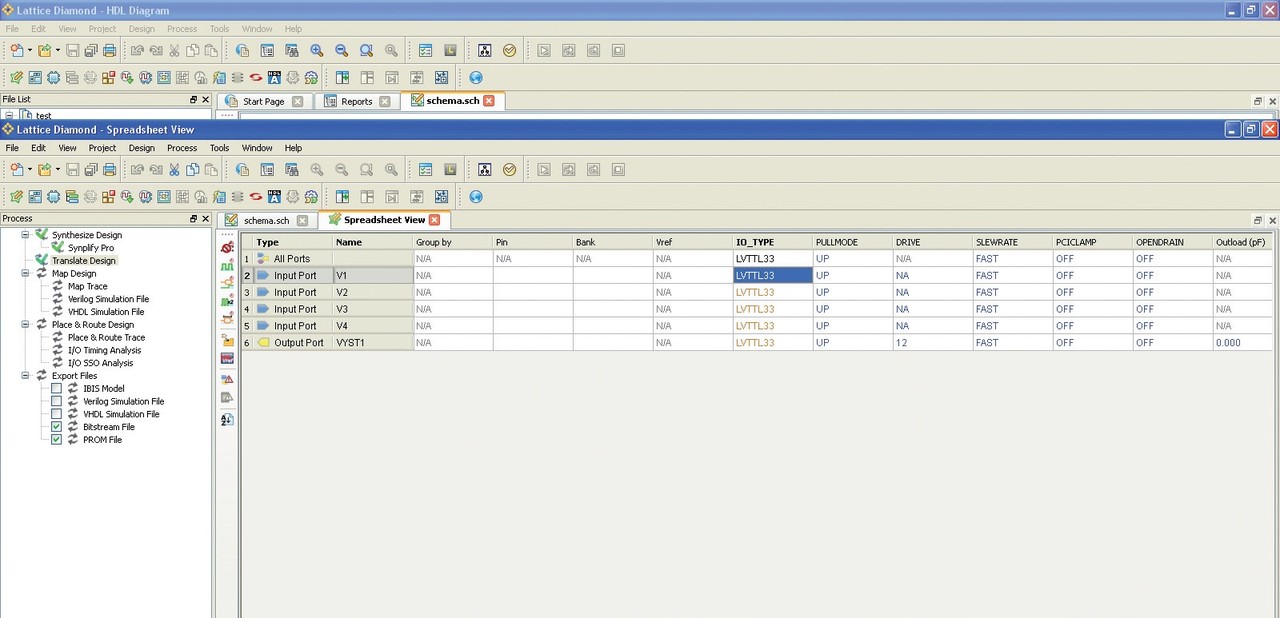

V levém okně vybereme záložku Process a zaškrtneme volbu, že chceme vytvořit PROM file. Nyní poklepeme na položku Translate design a po krátké práci programu vybereme ikonku Spreadsheet view. Zde lze nastavit většinu parametrů návrhu. Můžeme přiřadit čísla pinů pouzdra k jednotlivým spojům, terminaci vývodů atd. Nyní nastavíme parametry generovaného souboru pro programátor, kdy nastavíme čísla vývodů a napěťové úrovně (obr. 6).

Obr. 6 Nastavení parametrů návrhu

Poklepáním na položku PROM file již můžeme vygenerovat soubor pro programátor paměti. V tuto chvíli vidíme statistiku našeho návrhu. Je zde vidět, jak hodně jsme hradlové pole obsadili. Myslím, že tento údaj nepotřebuje komentář.

Number of registers: 0

PFU registers: 0

PIO registers: 0

Number of SLICEs: 1 out of 10584 (0%)

SLICEs(logic/ROM): 1 out of 8694 (0%)

SLICEs(logic/ROM/RAM): 0 out of 1890 (0%)

As RAM: 0 out of 1890 (0%)

As Logic/ROM: 0 out of 1890 (0%)

Number of logic LUT4s: 1

Number of distributed RAM: 0 (0 LUT4s)

Number of ripple logic: 0 (0 LUT4s)

Samozřejmě takto jednoduše si svůj vlastní procesor asi nevytvoříme. K tomu již musíme použít zabudované funkce simulace a použít VHDL. Také je nutné počítat s dobou šíření signálu uvnitř hradlového pole, vzít v úvahu možné hazardy atd. Na běžně používané věci s tímto postupem však vystačíme. Je tedy výhodou, že můžeme začít u jednoduchého invertoru a skončit třeba s polem procesorů. Je potřeba si ale uvědomit, že se také jedná o dobrý obchod. Složité návrhy hradlových polí se cenově pohybují v milionech dolarů, ale jako investice stačí počítač a integrovaný obvod v ceně několika stovek korun.

Na stránkách www.opencores.org lze nalézt ke stažení velké množství návrhů. Od jednoduchého návrhu např. kvadraturního dekodéru přes jednotky pro výpočet v pohyblivé řádové čárce až po 64bitový RISC procesor. Na závěr si ukážeme implementaci klopného obvodu řízeného hranou v jazyce VHDL:

library ieee;

use ieee.std_logic_1164.all;

entity klop is

port (

d,clk : in std_logic;

q : out std_logic;

);

end klop;

architecture struct of klop is

begin

process(clk)

begin

if clk‘event and clk=‘1‘ then

q<=d;

end if;

end process;

end struct;