Rozumět funkci budičů A/D převodníků se vyplatí

V celé řadě oblastí se stále častěji potkáváme se snímači. Potřeba zpracovávat analogové signály, včetně souvisejících analogově-číslicových převodníků (ADC, A/D), tedy neustále roste. Pro globální trh se senzory se také předpokládá složené roční tempo růstu přes devět procent. Expanze se přitom na koncových trzích týká různých aplikací internetu věcí, tovární automatizace a řízení, péče o veřejné zdraví a bezpečnost, zdravotnictví nebo též automobilového průmyslu. V případě A/D převodníků se pak ubíráme k lepšímu rozlišení a také vyšším rychlostem, protože jsou taková řešení cenově ještě dostupnější.

Co to je budič převodníku

Jak již název napovídá, budiče ADC jsou speciální zesilovače navržené především ke vzájemné spolupráci s A/D převodníky – ať se již bude jednat o architekturu s postupnou aproximací, pipeline, či delta–sigma. Takové úzce zaměřené zesilovače budou klíčovou součástí obvodového řešení umožňující převodníku pracovat naplno. S nástupem vyšších rychlostí a lepšího rozlišení pak u ADC jejich význam roste ještě více.

K otázce vstupů převodníku

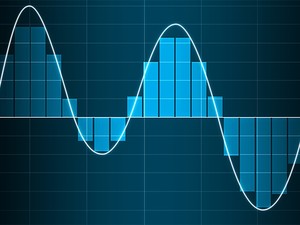

Dříve než se dostaneme k technickým vlastnostem vyžadovaným od budiče ADC, bude užitečné krátce se zaměřit na vstupní architekturu současných A/D převodníků. Rozdílový signál je možné definovat ve dvou bodech, u kterých máme sice stejné, ale jinak opačně orientované průběhy vztažené k pevně dané úrovni, kterou pak nazýváme souhlasnou. U zmíněných dvou signálů – míst − pak obvykle používáme výrazy, jako jsou kladný či záporný, resp. neinvertující a invertující – viz obr. 1.

Obr. 1 Příklad rozdílového sinusového průběhu signálu

V našem případě bude plné vstupní napětí špička–špička rozdílově činit 5 V, přičemž každá ze složek má rozkmit 2,5 V špička–špička. Souhlasná úroveň zde bude rovna 2,5 V. Většina současných ADC s lepšími parametry využívá právě rozdílové vstupní architektury, která v porovnání s jednoduchými vstupy nabízí lepší výsledky. Mezi její výhody zařadíme schopnost potlačit souhlasné rušení a také interference nebo i nárůst dynamického rozsahu o 6 dB (tj. na dvojnásobek).

A/D převodníky mohou pro vývojáře představovat obzvláště náročný úkol. Potkáváme se zde totiž s řadou různých vstupních architektur pro vzorkování, které je zapotřebí uvážit na systémové úrovni. Pro účely našeho pojednání se zaměříme na ADC, které na vstupu za účelem pořizování vzorků využívají strukturu se spínanou kapacitou. Takový vstup bude v nejjednodušší podobě složený z relativně malé kapacity společně s analogovým spínačem – viz obr. 2.

Obr. 2 Zjednodušená vstupní struktura převodníku se spínanou kapacitou

Pokud se spínač nachází v poloze č. 1, nabíjí se vzorkovací kondenzátor na napětí v příslušném bodě, které je v našem případě tvořeno VS. Spínač se poté přepne do pozice č. 2, kde bude náboj nahromaděný ve vzorkovacím kondenzátoru přenesen do zbývající části obvodu. Celý proces se pak znovu opakuje.

Vstup se spínanou kapacitou bez jakéhokoli bufferu jako je i ten popsaný výše může na systémové úrovni způsobit zásadní problémy. Proud potřebný k nabití vzorkovací kapacity na příslušné napětí totiž musíme dodat z vnějšího obvodu zapojeného ke vstupu ADC. Máme-li tedy spínač dle obr. 2 v první poloze a kondenzátor může vzorkovat, bude při spuštění nabíjení kapacity zapotřebí velkých proudů. Velikost okamžitého odběru je přitom funkcí velikosti vzorkovací kapacity, kmitočtu, na kterém kondenzátor spíná, a také napětí přítomného na vstupu. Proud během spínání lze proto vyjádřit následovně:

iin = CVf

kde C bude kapacitou vzorkovacího kondenzátoru, V představuje napětí přítomné v konkrétním bodě (v našem případě to znamená VS) a f bude konečně kmitočtem, na kterém spínač při vzorkování spíná a vypíná. Spínání bude mít na vstupu za následek velké proudové špičky, přesně jak to vidíme na obr. 2.

Při návrhu analogových obvodů zapojených před A/D převodníkem je proto zapotřebí zvážit možné důsledky proudu tekoucího spínačem. Teče-li takový proud jakýmkoli odporem, vzniká na něm úbytek napětí, který pak na vstupu ADC vnáší napěťovou chybu. Zkreslení se může rovněž vyskytnout, pokud se před dalším cyklem vzorkování vstup zcela neustálí.

Řešením jsou budiče převodníků

Zachovat v případě senzoru požadovanou integritu signálu a naplno přitom těžit z A/D převodníků s vyšším rozlišením a také větší rychlostí není vůbec jednoduché. Jakmile rozlišení a také rychlost ADC rostou, bude vliv šumu a také zkreslení, pokud jde o signál přicházející ze snímače, ještě patrnější. Při vyšších rychlostech vzorkování A/D převodníku je kromě toho zapotřebí pečlivě zajistit, aby se vstupní signál ustálil ještě před samotným vzorkováním. Signály s větší šířkou pásma nám rovněž nesmí zasahovat do pásma užitečného signálu.

Abychom se s těmito náročnými úkoly při zpracování signálu vypořádali, bude v řadě aplikací s ADC zapotřebí budič A/D převodníku, který zajistí adekvátní ustálení a také anti-aliasing. Jak jsme již naznačili, většina moderních ADC používá rozdílovou architekturu vstupu. Jednou z hlavních funkcí budiče převodníku pak bude zajistit konverzi jednoduchého příchozího signálu na rozdílový (i když stejně jednoduše si budou vědět rady i s rozdílovým vstupním signálem).

Další funkce budiče ADC spočívá v oddělení vstupního signálu, takže zbylé obvody izolujeme od injekce náboje na vstupu převodníku. Budič ADC poskytuje okamžitý náboj, aby se mohl vstup v dané době rovněž ustálit a minimalizovalo se jakékoli zkreslení, které souvisí právě s ustálením. Na úrovni desky je navíc zapotřebí věnovat pozornost layoutu v případě budiče ADC a také převodníku, kdy potřebujeme zajistit minimální odpor trasy vedoucí z výstupu budiče na vstup ADC.

Většina zesilovačů na pozici budičů A/D převodníků hardwarově také nabízí vývod, který vývojářům umožňuje posouvat úroveň souhlasného napětí. Taková funkce nám perfektně zajistí vystředění výsledného rozdílového signálu s ohledem na vstupní napěťový rozsah ADC, takže se maximálně využije dynamický rozsah. Provozní napětí se zmenšují a význam dynamického rozsahu při zajišťování plného rozlišení vstupního signálu zde proto ještě více roste.

Podobně jako většina zesilovačů v podobě součástek mohou nakonec i budiče A/D převodníků vyřešit zesílení vstupního signálu, stejně jako aktivní filtraci. Dlužno však dodat, že většina budičů ADC mívá specifikace s relativně malým ziskem, typicky pouze 1 či 2 V/V. Pokud se u zesilovače udrží nízké zesílení v uzavřené smyčce, maximalizuje se zisk smyčky a znamená to nejmenší zkreslení. Jestliže má např. zesilovač zisk v otevřené smyčce 100 dB a bude přizpůsoben pro zesílení v uzavřené smyčce 200 nebo 46 dB, dostaneme rozmezí pro zajištění linearity, pokud jde o zesílení v otevřené smyčce, pouze 54 dB nebo zhruba jedna ku pěti stům. Je proto běžné mít samostatný zesilovací stupeň, který je umístěn poblíž zdroje signálu, abychom maximalizovali odstup signál–šum.

Díky rozšiřování senzorů v celé řadě oblastí se obvodům pro zpracování signálu dostává ještě větší pozornosti. S tím, jak cena A/D převodníků s vysokým rozlišením a také vyšší rychlostí postupně klesá, bude ale náročnější podobná zlepšení vlastností realizovat.

Abyste proto ze svého A/D převodníku vytěžili maximum, bude při optimalizaci vlastností hrát klíčovou roli právě budič ADC, který by měl do zdrojového signálu vnášet jen zcela nepatrné zkreslení, šum nebo i chyby spojené s dobou ustálení. Za účelem dosažení maximálního výkonu vysokorychlostních A/D převodníků s vysokým rozlišením byly již konkrétně navrženy speciální obvody, jako je např. rozdílový budič MCP6D11 [1].

Odkazy:

[1] Obvody MCP6D11, https://www.microchip.com/wwwproducts/en/MCP6D11