Realizace jednoduchého rozhraní sběrnice PCI

Motivace

- Moderní komponenty pro osobní počítače mají stále vyšší nároky na rychlost komunikace a široce rozšířené rozhraní ISA, dříve přítomné v každém PC, bylo vytlačeno sběrnicí PCI. Není již tak jednoduché navrhnout aplikační desku do PC, jak tomu bylo u sběrnice ISA.

- Jeden z našich produktů – desku do PC s pracovním názvem Archiv – bylo nutno redesignovat po hardwarové stránce ze sběrnice ISA na PCI s požadavkem na maximální možnou kompatibilitu s již existujícím softwarem běžícím v PC.

Jak se vývojáři ve firmě Ryston s tímto problémem vyrovnali, je popsáno v následujícím článku.

Původní produkt

Archiv je vestavná deska do technologického počítače sloužící jednak pro archivování záznamů o událostech nastalých při běhu programu, jednak pro připojení specifického zařízení přes 8bitový, galvanicky oddělený port. Deska má rozhraní sběrnice ISA (8 bitů, kompatibilní s PC XT/AT).

Jednotka obsahuje zálohovanou statickou RAM s kapacitou 4 až 16 MB, připojenou přes rozhraní podobné řadiči pevného disku, kde adresa „sektoru“ je tvořena třemi přednastavitelnými čítači. Do těchto čítačů je možno programem vstoupit jako do paralelních registrů.

Obvody rozhraní sběrnice (původně řada 74LS) byly nahrazeny programovatelným logickým obvodem. Zálohovací obvod s baterií v době výpadku externího napájení zaručuje uchování dat ve statické RAM po dobu až několika let.

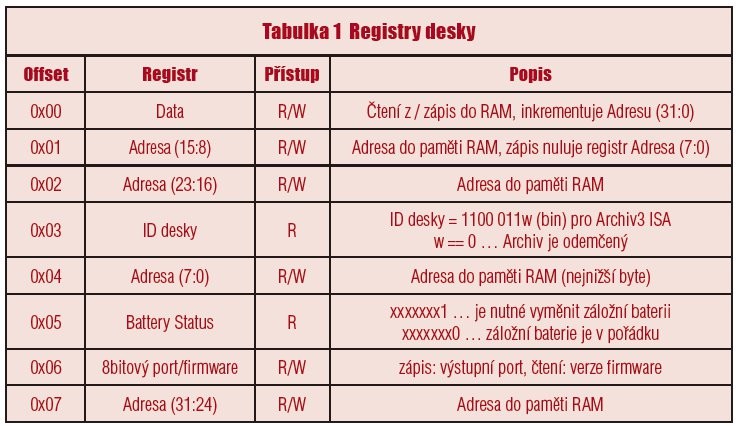

Karta se chová jako 8 registrů v I/O adresním prostoru PC, jejichž bázová adresa je určena nastavením přepínače DIP v rozsahu adres 1C0 až 1F8, zpravidla neobsazených žádnou periferií. Každý registr je přístupný na adrese bázová adresa + offset podle následující tabulky.

Tabulka 1 Registry desky

Zápisem do 4 registrů se nastaví až 32bitová adresa (počátek „sektoru“ – oblasti přístupu) a následujícím zápisem nebo čtením datového registru se zapíše nebo přečte 1 byte dat z této adresy. Adresa se automaticky inkrementuje po každém zápisu nebo čtení datového registru. Adresa se skládá ze 4 registrů na offsetech 0×07, 0×04, 0×01, 0×02. Výstupy těchto registrů napájejí lokální adresovou sběrnici. Datová sběrnice, využívaná přístupem do adresy 0×00, je obousměrná. Registry Status a ID jsou pouze čtecí.

Rozdíly ISA versus PCI

Sběrnice ISA má šířku dat 8 nebo 16 bitů a adresní prostor 20 nebo 24 bitů. Data jsou přenášena během aktivace příslušného signálu Read nebo Write. Transakce sběrnice nejsou synchronní s taktovacími hodinami (4,77 až 8,3 MHz). Případné konflikty periferií, které by obsazovaly stejné adresy, se řeší nastavováním propojek určujících bázovou adresu desky, anebo u moderních desek metodou Plug and Play (PnP), která je z hardwarového pohledu poměrně složitá. Sběrnice ISA nebyla nikdy celosvětově standardizována, a rozdílné realizace výrobců tak nemusí být vždy kompatibilní. Ze sběrnice ISA pochází několik derivátů s rozšířenou adresací (Vesa apod.), které se krátkodobě používaly, ale byly opuštěny.

Specifikace PCI protokolu byla vyvinuta a je udržována společenstvím PCI-SIG, které má globální rozsah a respekt. Tato sběrnice je orientována na přenos zpráv (transakcí) místo přímého zápisu a čtení dat a používá multiplexaci adresních a datových signálů. Každá transakce obsahuje inicializaci, adresní část, datovou část s případnými čekacími cykly a zakončení. Jednotlivé části transakce probíhají synchronně rychlostí 33 MHz nebo 66 MHz (určeno nejpomalejším zařízením) a šířkou dat 32 nebo 64 bitů.

V zařízení (periferní desce) musí být implementována konfigurační paměť, která slouží pro uložení bázové adresy, podporované šíře datové sběrnice, počtu čekacích cyklů apod. Tento mechanismus je podstatně lepší než ISA PnP.

Sběrnice PCI je tedy podstatně rychlejší než ISA, vyžaduje však velmi složitý řadič. Existuje řada provedení integrovaných řadičů s lokální sběrnicí, ale jsou poměrně drahé a nesplňují požadavek kompatibility s původní deskou.

Implementace jednoduchého PCI rozhraní

Rozhraní sběrnice desky Archiv je realizováno v hradlovém poli typu CPLD. V případě ISA sběrnice je realizace několika 8bitových registrů a řídicí logiky nenáročná na prostředky hradlového pole, a tak bylo možné použít obvod MAX3064 (od firmy Altera).

Vývoji desky Archiv nové verze předcházel podrobný základní výzkum rozhraní PCI až na úroveň bitů konfiguračního prostoru a jejich významu, i nedokumentovaného v originální specifikaci [1], avšak podporovaného PCI BIOSem a popsaného v další literatuře [2]. Deska se z pohledu PC chová jako PCI zařízení podporující pouze 8bitový přístup do I/O prostoru. Jádro firmware vychází ze specifikace PCI 2.1 [1].

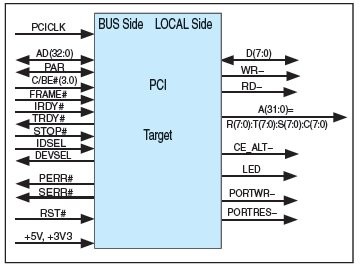

Popsané rozhraní je typu Target, což znamená, že je vždy podřízeno sběrnici. Proto je většina řídicích signálů znázorněna jako vstupy do rozhraní (z levé strany). Na pravé straně (lokální) je 8bitová obousměrná datová sběrnice a výstupy adres a řídicích signálů do desky.

V rozhraní se nachází poměrně složitý automat, taktovaný signálem PCICLK, který reaguje na oslovení desky ze strany sběrnice signály FRAME#, C/BE# a AD, odpoví aktivací signálu DEVSEL#, vloží několik čekacích period a potvrdí transakci aktivací signálu TRDY#. Rozhraní generuje a kontroluje paritu přes signály AD a C/BE# a případnou chybu hlásí přes PERR#. Typ transakce (např. zápis do portu) je určen kombinací čtveřice signálů C/BE#. Pro podrobný popis chování sběrnice PCI odkazujeme na [1].

Na straně lokální sběrnice je vygenerován cyklus odpovídající demultiplexované sběrnici Intel a dekódují se příslušné selekty pamětí (zálohovací mechanismus pomocí signálu CE skrz obvod Dallas, zde neznázorněno) nebo zápisové impulsy do portu. Tato lokální strana může být snadno modifikována podle jiných uživatelských požadavků.

Co se děje v počítači po zapnutí

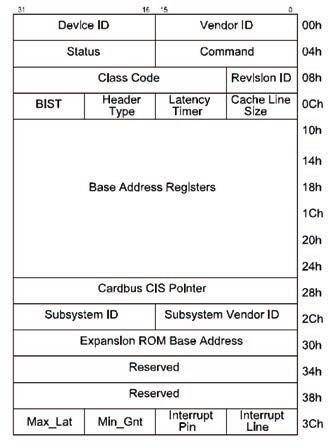

Deska vložená do PCI slotu je po zapnutí napájení nebo resetu rozeznána PCI BIOSem, který má přístup do konfiguračního prostoru desky. V něm je viditelná datová struktura s několika pozicemi, popisujícími výrobce a typ desky/řadiče a další vlastnosti: Device ID, Vendor ID, Class Code.

PCI BIOS automaticky nastaví kartě bázovou adresu (čtecím/zápisovým mechanismem do registru BAR v konfiguračním prostoru zařízení), avšak na rozdíl od „čisté“ specifikace je v naší BAR hodnota předdefinována a read-only, a tak je BIOSu „vnucena“ deskou stejná bázová adresa jakou měl původní Archiv.

Obr. 1 Blokové schéma rozhraní PCI

Obr. 2 Konfigurační prostor desky PCI

Pro implementaci stavového automatu, který realizuje protokol transakcí sběrnice PCI, bylo nutné použít modernější obvod EPM570, který obsahuje cca desetinásobné množství logických elementů než obvod MAX3064.

Specifikace [1] předepisuje na svých 400 stranách řadu mechanických a elektrických parametrů. Jedním z nejdůležitějších je délka přívodů mezi konektorem a obvodem řadiče a zejména je předepsána délka vodiče signálu PCICLK (synchronní hodiny) a jeho impedanční přizpůsobení sériovým rezistorem pro potlačení zákmitů. U signálů sběrnice, delších na desce než cca 5 cm, jsou doporučeny rovněž sériové rezistory 22 Ohmů. V našem případě byla pečlivým návrhem plošného spoje dodržena minimální délka vodivého obrazce, a proto rezistory nejsou třeba, s výjimkou hodinového signálu.

Pro snížení spotřeby v zálohovacím (spacím) režimu je na lokální straně přizemněna datová a adresová sběrnice. Zjistili jsme, že statické paměti dramaticky zvyšují svoji spotřebu ve spacím režimu, pokud jejich sběrnice není trvale v nízké logické úrovni. Protože při výpadku napájení jsou výstupy obvodu CPLD nedefinovány, byly doplněny tyto pull-down odpory.

Zpětná kompatibilita

Kvůli specifickým požadavkům zákazníka na absolutní zpětnou kompatibilitu se softwarem, který byl napsán pro přístup k Archivu s rozhraním ISA, bylo nutné maličko porušit specifikaci, jak bylo popsáno výše. Bylo to však ke spokojenosti zákazníka. Návrh CPLD však variantně umožňuje i zcela čisté chování při identifikaci. Dosud nebyl zaznamenán žádný konflikt, ani na schválených modelech technologického počítače, ani jinde.

Výsledkem je deska Archiv PCI, která obsahuje stejnou nebo až 4× větší kapacitu paměti než verze ISA, a která po proběhnutí inicializace a využití „nuceného“ obsazení bázové adresy se vůči aplikačnímu softwaru tváří identicky jako původní deska. Aplikační SW tak bylo možno ponechat bez jakékoli změny.

Co bylo nerealizováno, a co naopak přidáno

Především nebyl realizován přenos dat v plné šíři 32 bitů. Přesněji řečeno přístup do samotného obvodu řadiče je 32bitový, ale data do paměti jsou v souladu s původní specifikací jen 8bitová. Znamená to, že datový přístup do desky skrz řadič je umožněn jen z adresy, jež je dělitelná 4, ale tomu naštěstí vyhovuje původní struktura registrů, kdy data jsou na adrese base+0.

Samotný software samozřejmě je poněkud nekorektní, protože by měl přistupovat do desky prostřednictvím ovladače pod operačním systémem – to však je přesně to, co uživatelé nechtěli.

Dále nebyla implementována funkce PCI „Master“, kdy procesor na desce se skrze řadič zmocní sběrnice a provádí na ní svoje transakce. Naše deska toto nikdy nežádá, protože na sobě nemá procesor.

A konečně, nebyla realizována funkce „spánku“ počítače. V dané aplikaci počítač běží neustále v aktivním režimu, takže to nevadí.

Obr. 3 Foto desky PCI archivu

Protože po implementaci velmi minimalistické verze PCI protokolu zbyly v hradlovém poli ještě nějaké nevyužité prostředky, rozhodli jsme se dle přání zákazníka rozšířit zařízení Archiv o přístup přes rozhraní USB. To umožňuje provádět stejné operace např. pomocí externího notebooku při přítomnosti Archivu ve vypnutém PC nebo mimo něj, a vyčítat tak archivovaná data. Provedený výzkum a následná realizace USB rozhraní s využitím obvodu FT245 budou popsány v některém z příštích článků.

Možnosti dalšího využití

Popsané PCI rozhraní „chudého muže“ je asi to nejjednodušší, co lze vytvořit, aby to prošlo testem PCI BIOSu. Od té doby jsme vyvinuli řadu modifikací a vylepšení pro větší průchodnost a s integrovanou aplikační logikou v stejném pouzdru CPLD. Zdrojový kód byl napsán v jazyce VHDL.

Poznatky a techniky využité v rozhraní PCI desky Archiv je nyní možno využít ke konstrukci jednoduchých aplikačních desek do PC, jako např. převodníky, komunikace, kryptografie, laboratorní přístroje a další.

Obvod CPLD je poměrně levný a má dostatečnou kapacitu pro realizaci dodatečné logiky nebo automatu potřebného vnitřkem desky. I když v desce Archiv se používá 4vrstvý plošný spoj, bylo odzkoušeno i použití 2vrstvého materiálu, vhodného pro vývoj i téměř amatérských desek plošných spojů.

Literatura

[1] PCI Local Bus Specification rev. 2.1s, PCI Special Interest Group, P.O.B. 14070, Portland, OR97214, USA

[2] Goodrum, A.: PCI Hot-Plug Application and Design. Annabooks, 11838 Bernardo Plaza, San Diego, CA 92128, USA