Před rokem byl vyvinut ve firmě Ryston Electronics testovací a měřicí systém osazených DPS metodou JTAG. Tento systém byl rozvinut a využit pro výrobní testy palubní vozidlové jednotky (OBU) při předsériové výrobě v množství asi 1 000 kusů pro odladění náběhu výroby řádu stovek tisíc kusů ročně. Toto množství již vyžaduje minimalizaci ruční práce, sledování doby zkoušek, testování a programování obvodů na několika vyrobených deskách (panelu po čtyřech) paralelně, a samozřejmě též totální napojení na systém řízení jakosti výrobce.

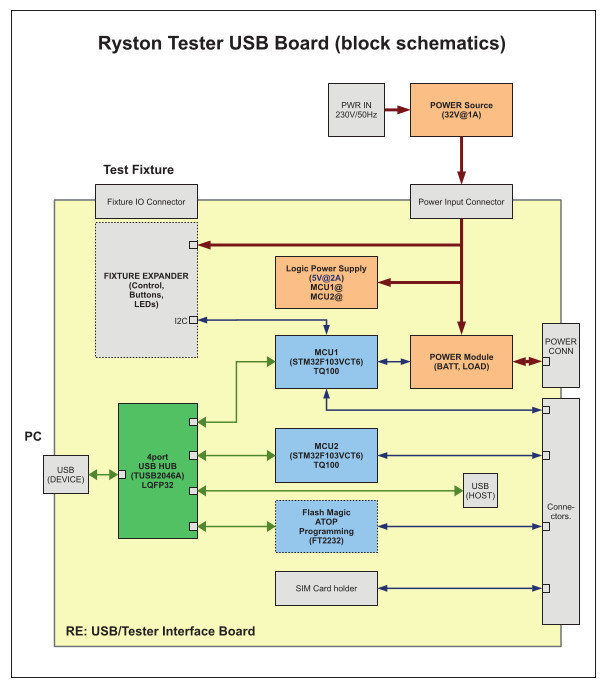

Systém nové generace je tvořen sadou desek s rozhraním USB, řízenou paralelně z PC přes USB porty (kolik desek se paralelně testuje, tolik desek rozhraní). Na desce rozhraní je integrovaný USB hub a řada převodníků USB na SPI, RS232 a další rozhraní, dále napájecí vstup a řiditelné zdroje s měřením proudu, elektronická zátěž s měřením a jako rezerva připojení na externí multimetr a rozhraní k samotné testované desce přes fixturu s polem testovacích hrotů.

Na desce je dále řada adaptérů na konektory testované desky s digitálním, popř. analogovým, rozhraním, generátor časových průběhů a identifikační obvody pro snadnou výměnu desky v případě poruchy. Součástí systému je PC a jeho programové vybavení, jednak pro online řízení testeru, jednak pro přípravu testů.

Testovací systém dovoluje přímo zkoušet desky obsahující čipy s JTAG rozhraním. Pro oblast pokrytou JTAGem je možno snadno, téměř automaticky generovat testy na základě BSDL souborů popisujících JTAG strukturu obvodů a jejich pořadí v JTAG řetězci. Umožňuje však nepřímo zkoušet i subsystémy mimo toto rozhraní, avšak příprava testu je komplikovanější.

Tento systém dokáže v přímém módu najít následující chyby na desce:

Přímý mód JTAG umožňuje otestovat části desky tvořené nejčastěji hustě montovanými BGA součástkami s mnohavodičovým propojením (např. 32bitovou sběrnicí), které prakticky nelze testovat jinak.

V nepřímém módu je nadto možno nalézt následující chyby:

Nepřímé módy tedy většinou umožňují nalézt chyby i v oblasti nepřístupné přímo JTAGu, např. v analogové síti, ale příprava testů je komplikovanou inženýrskou záležitostí, protože tvůrce testu musí znát schéma a funkci těchto obvodů a často je třeba vyrobit různé přípravky.

Dále jsou zde testy nepracující se systémem JTAG (např. měření odběrů, dobíjení, zátěže), ale mohou s JTAG testy být „proloženy“, protože například je nejprve nutno naprogramovat pomocný procesor, pak ho spustit a otestovat jím řízený napájecí a dobíjecí systém pro akumulátor simulovaný zátěží. Poté se přejde k JTAG testu podřízeného digitálního systému.

Nelze testovat například oscilátory nebo vysokoimpedanční obvody, lze jen nepřímo (pomocí děličky nebo squelch obvodů) odvodit informaci o jejich funkci.

Programové vybavení pro řízení testovacího adaptéru pracuje např. pod Windows XP a skládá se z několika programů.

Pracující offline (příprava testů a zpracování výsledků):

Online program:

Tester připojený na fixturu s měřicími hroty pro panel se čtyřmi deskami byl nasazen ve výrobní hale na výstup pájecí linky. První verze ostrého testovacího a programovacího softwaru požaduje na běh 2 minuty, během nichž provede u čtyř desek najednou přezkoušení funkce dohledového procesoru, naprogramování, kontrolu zdrojů a dobíjecího obvodu baterie a elektrický test hlavního procesoru, paměti a většiny konektorů. To umožnilo během dvou pracovních dnů osadit, zapájet a otestovat 600 základních desek vozidlové jednotky nesoucích kolem 600 součástek. Chybovost byla pod 1 % (5 desek) a z nich bylo možno opravit 3 desky, které pak prošly testem.

Panely byly po testu opatřeny identifikačními štítky a rozlámány na samostatné desky, které byly doosazeny přídavnými moduly do objímek a konektorů (např. SIM, OLED displej), byly vloženy do plastového pouzdra, připojen kabel k baterii a na závěr byl proveden funkční test s lidskou obsluhou a simulátorem vf signálů.

Instalací tohoto testeru na výstupu osazovací a pájecí linky u našich zákazníků byla zajištěna oživitelnost pilotní série osazených desek. Při jediném založení panelu do testovací fixtury se provede test a naprogramování, což šetří další montážní operace. Tento systém dává předpoklady pro úspěšné rozjetí sériové výroby, kterou plánujeme.

Testovací systém je možno zaintegrovat do systému řízení kvality, a tak získávat automaticky jednotlivá i statistická data o zkouškách, a dále umožňuje programovat software nebo obsah EEPROM individuálně do desek dle jejich identifikátoru, čímž lze řešit licencování instalací a individualizaci jednotek. Na tom se bude v budoucnu pracovat.