Výkonné ZVS regulátory s širokým rozsahem vstupního napětí

V moderních elektronických systémech se můžeme stále častěji setkat s potřebou vyššího výkonu a účinnosti, tvořené pomocí neizolovaného Point-of-Load (niPOL) regulátoru. Tedy DC/DC regulátoru s jediným převodním stupněm. Jednou z možností, která se dnes konstruktérům elektronických systémů pro zvýšení účinnosti nabízí, je eliminace vícestupňové konverze a použití niPOL regulátoru přímo na požadované napětí. To znamená, že zvolené regulátory pracují při vyšším vstupním napětí a s vyšším převodním poměrem, než na jaké jsme byli ještě donedávna zvyklí. Dalším požadavkem na niPOL je samozřejmě udržení co možná nejvyšší účinnosti a současné zmenšení celkových rozměrů bloku napájecího zdroje. Mimo to je však často nutné počítat také s určitou výkonovou rezervou, potřebnou pro vykrytí změn v odběru dané aplikace (tedy zvýšením výkonu niPOL).

Výsledkem je řada reakcí průmyslového segmentu a zavedení mnoha technologických změn v oblasti niPOL regulátorů. Pohledem do historie přitom snadno zjistíme, že především v několika posledních letech došlo v této oblasti k celé řadě změn v podobě dokonalejších pouzder s lepším odvodem tepla, integrací křemíkového čipu a použití nových technologií výroby spínacích prvků typu MOSFET. Cílem je přitom snadná dostupnost vysoce integrovaných, kompaktních řešení s dostatečným výkonem a rozsahem provozních hodnot. Zatímco v případě úzkého rozsahu napětí jsou požadavky na výkon a účinnost splněny prakticky libovolným DC/DC regulátorem, mnohem horší situace nastává v okamžiku rostoucího poměru mezi vstupním a požadovaným výstupním napětím. Již hodnoty 10:1 nebo 12:1 představují obvykle vážnější problém a přímo dramatické zhoršení nastává v okamžiku opravdu velkého rozdílu napětí s poměrem kupříkladu 36:1 a více.

V posledních letech se tak v případě niPOL regulátorů odehrála hned celá řada změn, ovšem v případě hlavního spínacího obvodu byly zaznamenány nejmenší změny. Dnes je znám nespočet modifikací řídicí topologie, jako jsou řízení v proudovém režimu, simulovaný proudový režim, digitální řízení atd. nebo návrhy na zvýšení výkonu pomocích usměrňovačů a adaptivních budičů. Všechna tato řešení mají však obvykle za následek pouze dílčí zlepšení a/nebo výrazné zvýšení složitosti konstrukce.

Snižující regulátor s přímým řízením vstupního napětí sám o sobě poměrně značně omezuje možnosti zlepšení výkonu a použití v širokém rozsahu provozních hodnot. Zmenšení velikosti napájecího zdroje lze docílit obvykle pouze redukcí hlavních prvků systému. Nejlepší způsob, jakým toho lze dosáhnout, je jednoduché zvýšení spínací frekvence. S tím je však v praxi spojena hned celá řada problémů. Zvýšení spínací frekvence v případě přímého řízení výstupního napětí by se tak dalo přirovnat například ke snaze zvýšení výšky děravé přehrady.

V praxi jsou dostupné především tři základní možnosti:

- Přímé řízení: Simultánní řízení proudu pomocí spínání vysokého napětí na vstupní straně napájecího zdroje je příčinou frekvenčně a napěťově závislých spínacích ztrát a zároveň přímou překážkou provozu v širokém rozsahu vstupního napětí. Nová technologie výroby spínacích tranzistorů typu MOSFET s dokonalejším FOM (Figures of Merit) umožňuje použití vyšších spínacích frekvencí. Ovšem i to je zdrojem hned celé řady problémů, mezi které patří především vznik nežádoucích napěťových špiček (plynoucích z podstaty přímého řízení), zvýšení EMI i dokonalé uzavření spínacích prvků, které je třeba řešit. Všechny tyto a mnoho dalších problémů je tím výraznějších, čím vyšší vstupní napětí a spínací frekvence jsou v obvodu napájecího zdroje použity. Z toho plyne, že použití vyšší spínací frekvence a širšího provozního rozsahu nejdou dohromady.

- Integrovaná dioda: Topologie synchronního spínače a dioda, která je vždy součástí vnitřní struktury tranzistorů MOSFET, jsou rovněž zdrojem nižší účinnosti a v případě vysoké spínací frekvence mohou být poměrně značně limitující. Integrovaná dioda ovlivňuje obvod vždy ve chvíli změny, tedy jak v okamžiku sepnutí, tak i vypnutí daného tranzistoru MOSFET.

- Ztráty v Gate: Spínání tranzistorů MOSFET vysokou frekvencí způsobuje také nárůst ztrát v obvodu řízení elektrody Gate.

Tento článek se s použitím simulačních modelů snaží přiblížit možnosti konstrukce spínaných napájecích zdrojů s vysokou pracovní frekvencí a porovnat dvě základní topologie konvenčních snižujících regulátorů. Bude představena nová topologie snižujícího regulátoru „ZVS Buck“ jakožto součást rodiny produktů Picor Cool-Power® ZVS Buck. Na simulačním modelu nového ZVS Buck regulátoru si navíc ukážeme, na jakém principu ZVS (Zero-Voltage-Switching) topologie vlastně pracuje a proč dosahuje tak vysokých hodnot výkonu, účinnosti a širokého rozsahu provozních hodnot bez výraznějšího vlivu na jeho vlastnosti. Topologie ZVS Buck regulátorů má mnoho výhod, které budou spolu s teorií provozu dále popsány.

Simulační model

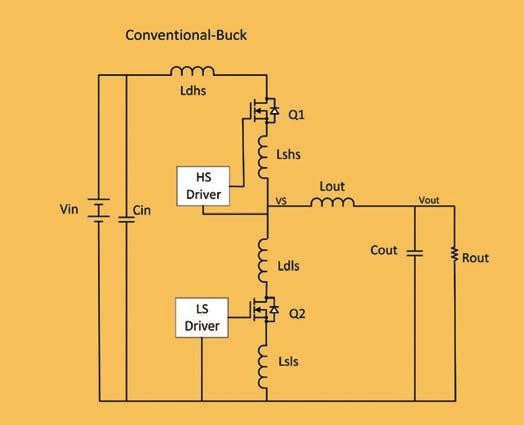

Na obrázku 1 je uveden zjednodušený model typického snižujícího regulátoru, včetně parazitních indukčností, které jsou součástí jak tranzistoru MOSFET, tak i samotných spojů na DPS. V zájmu analýzy skutečných limitujících faktorů těchto napájecích zdrojů při vyšších frekvencích byl simulační model postaven za použití nejlepších tranzistorů MOSFET ve své třídě (a dostupných SPICE modelů).

Obr. 1 Topologie konvenčního snižujícího regulátoru

V našem případě budeme uvažovat o převodníku pro vstupní napětí minimálně 36 V a výstupní napětí 12 V s proudem při plné zátěži do 8 A. Simulace byly provedeny se spínací frekvencí 650 kHz při použití 2 mH indukčnosti a 1,3 MHz při použití 1 mH indukčnosti. Vnitřní odpor tranzistoru MOSFET ani při plné zátěži nepřekročil hodnotu 10 mΩ. Hodnota čtyř parazitních indukčností Lshs byla stanovena na 300 pH a hodnota dalších indukčností na 100 pH. Všechny tyto parazitní indukčnosti jsou však silně závislé na zvoleném typu pouzdra, rozmístění součástek na desce s plošnými spoji či použití napájecí topologie (PSiP) Power-System- -in-Package. Budič tranzistorů obsahuje výstupní odpor v hodnotě 4 Ω (aby se nám minimalizovalo zvlnění) a oba tranzistory jsou navíc opatřeny odporem 1 Ω, zajišťujícím jejich rychlejší rozepnutí.

Přímé řízení

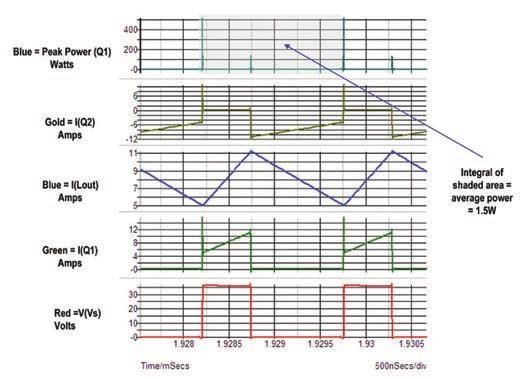

Na obr. 2 je uveden výsledek simulace okamžitého ztrátového výkonu na tranzistoru MOSFET Q1, napětí v bodě VS a průběh proudu na Q1 (zeleně), Q2 (červeně) a výstupní indukčnosti (modře).

Obr. 2 Simulace 650 kHz s rastrem 500 ns/div

Na výsledcích simulace je dobře vidět, že velmi vysoké ztráty se uplatňují především v okamžiku zapnutí tranzistoru a mnohem menší ztráty jsou poté pozorovatelné v okamžiku jeho vypnutí. Oblast mezi těmito body je ovlivněna především hodnotou RDS(on), která je však sama o sobě zdrojem pouze minimálních ztrát. Největší zásluhu na tom mají samozřejmě moderní tranzistory MOSFET s výrazně redukovanou hodnotou RDS(on), které v aplikacích tvoří pouze minimální ztráty vedením a umožňují tedy další operace. Podíváme-li se na celý spínací cyklus jednoho tranzistoru MOSFET, dojdeme k průměrné hodnotě ztrátového výkonu 1,5 W při 650 kHz. Tato hodnota se skládá z 0,24 W ztráty ve vedení, 0,213 W při vypnutí a 1,047 W při zapnutí. Hlavním původcem ztrát v případě Q1 je tedy okamžik sepnutí.

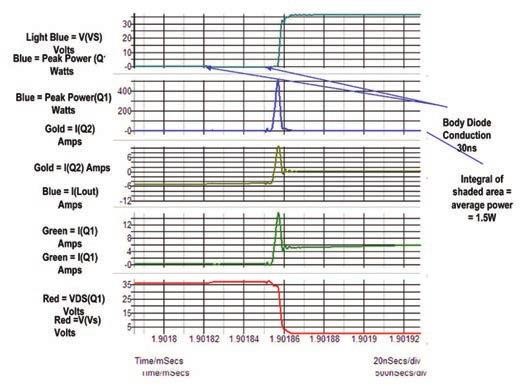

Obr. 3 Detail simulace 650kHz zotavovacího efektu s rastrem 20 ns/div

Na obr. 3 je detail oblasti těsně před a včetně přední hrany okamžiku sepnutí tranzistoru MOSFET Q1. K dispozici je 30 ns tzv. mrtvého času mezi vypnutím Q2 a zapnutím Q1. Jeho úkolem je eliminace toku nežádoucích proudů mezi (ne zcela) otevřenými/zavřenými tranzistory v můstkovém zapojení. Důsledkem toho však musí integrovaná dioda odvést zbytkový proud z výstupní indukčnosti. Během této doby je v provozu dioda tranzistoru Q2 a na jejím PN přechodu tedy dochází k akumulaci značné energie. Tento náboj však musí být odveden ještě dříve, než dioda začne blokovat zpětné napětí. Celému tomuto procesu se v praxi říká doba zotavení (nebo také anglicky Reverse Recovery).

Na obrázku 3 je vidět poměrně vysoká úroveň napětí mezi elektrodami Source a Drain Q1 (blížící se hodnotě VIN), ovlivněná parazitní indukčností spojů v okamžiku, kdy přes diodu v Q2 protéká vysoký proud. Špičkový (ztrátový) výkon je v tom okamžiku opravdu velmi vysoký, neboť Q1 musí odvést zotavovací náboj vnitřní diody Q2, zatímco je současně vystaven téměř plnému vstupnímu napětí. Ani parazitní indukčnosti Source Q1 (Lshs) nemají v tomto okamžiku příliš velký vliv. V okamžiku sepnutí tranzistoru MOSFET Q1 tento proud způsobí náhlý pokles napětí. Jelikož je tento úbytek napětí v opačném směru, tlačí napětí na Source proti řídicí elektrodě Gate, zatímco se řídicí obvod snaží překonat vliv Millerova efektu. To má za následek pohyb delší dobu v Millerově oblasti a z toho plynoucí vyšší výkonové ztráty na tranzistoru MOSFET Q1 a jeho řídicích obvodech. Důsledkem toho však může být také to, že tranzistor Q1 se nemůže dostat do plně otevřeného stavu do doby, než dojde k vybití a zániku blokování napětí diodou v Q2. Během této doby dosahuje zotavovací proud nejvyšší hodnoty a celý ztrátový výkon je veden pouze diodou v Q2, protože je tvořen napětím a proudem opačné polarity. Konec působení ztrátového výkonu v diodě je až v okamžiku dokončení rekombinace obou můstkově uspořádaných tranzistorů.

Obr. 4 Simulace 650 kHz s rastrem 20 ns/div a ovlivnění Gate zvýšením indukčnosti Lshs na 500 pH

Mírného omezení ztrátového výkonu Q1 lze dosáhnout použitím rychlejšího budiče. Silnější buzení elektrody Gate Q1 zajistí rychlejší přechod přes lineární oblast, a tím i vyšší zotavovací proud diodou Q2. Výsledkem však bude také rychlejší skoková hrana v bodě VS kvůli dostatečné zásobě energie v parazitních indukčnostech. Na obrázku 4 je vidět simulace řízení elektrody Gate při frekvenci 650 kHz a účinek Lshs na buzení Q1 při změně z 200 pH na 500 pH. Všimněte si změny na Q2 v okamžiku náběžné hrany v VS. Navíc kvůli Millerově kapacitě v Q2 dojde k přenosu skokové změny dV/dT v bodě VS rovněž na řídicí elektrodu Gate. Není těžké si pak představit efekt nárůstu u Q1. Rychlejší skoková změna dv/dt způsobí větší změny v Gate Q2, a tudíž jen další zvlnění. Pokud je Q2 provozován na nízkém napětí a s malým řídicím napětím, může dojít k jeho krátkodobému sepnutí vlivem napěťových špiček. Tento stav pak může, ale nemusí být nutně destruktivní. V každém případě však povede ke zhoršení celkové účinnosti napájecího zdroje. Vyšší energie uložená v parazitních indukčnostech může být rovněž zdrojem vysokého napětí na tranzistorech a v krajních případech může vyžadovat i řešení pomocí srážecích prvků.

Vyšší provozní frekvence

V dalším kroku jsme simulací ověřili tentýž model regulátoru při shodném výstupním proudu, ale s menší výstupní indukčností a na dvojnásobné spínací frekvenci. Jiné změny nebyly v daném modelu provedeny. Při spínací frekvenci 1,3 MHz se již celkové ztráty v tranzistoru Q1 MOSFET zvýšily na 2,73 W, a jak se dalo i očekávat, zapínací a vypínací ztráty jsou ve srovnání se simulací 650 kHz zhruba dvojnásobné. RMS proud v Q1však zůstal stejný, takže ztráty ve vedení se prakticky nezměnily.

Vzhledem k tomu, že největší ztráty vycházejí z Q1, bude zdvojnásobení spínací frekvence znamenat pokles účinnosti minimálně o 1,2 %. Vliv na celkovou účinnost je však tím vyšší, čím vyšší je konverzní poměr napájecího zdroje. Je tedy jasné, že tento přístup není nejlepší cestou ke snížení velikosti a zvýšení výstupního výkonu. Pokud tedy chceme zmenšit rozměry bloku napájecího zdroje a zároveň také zvýšit výstupní výkon, je třeba se v první řadě zabývat spínacími ztrátami, které se zvyšující se spínací frekvencí výrazně rostou.

ZVS topologie

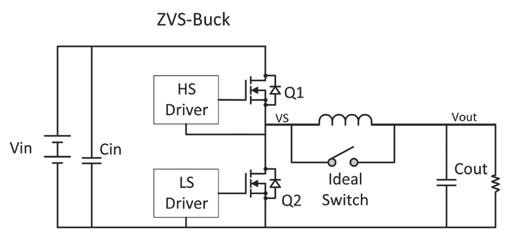

Obr. 5 znázorňuje zjednodušené schéma topologie snižujícího ZVS regulátoru. Schéma je prakticky identické s konvenčním snižujícím regulátorem, avšak kromě přidaného spínače, připojeného paralelně k výstupní indukčnosti. Spínač je určen k eliminaci energie akumulované ve výstupní indukčnosti a v ideálním případě by měl mít nulový odpor.

Obr. 5 Topologie ZVS regulátoru

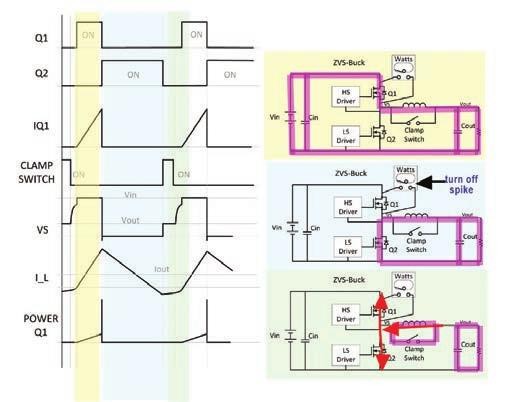

Topologie ZVS regulátorů vychází ze tří hlavních stavů. Těmi jsou fáze sepnutí Q1, fáze sepnutí Q2 a fáze odvodu. Abychom snáze pochopili, jak funguje spínač na výstupní indukčnosti, budeme předpokládat, že Q1 sepne při téměř nulovém napětí po odeznění rezonančních zákmitů. Q1 tedy spíná při nulovém proudu a v okamžiku, kdy je napětí mezi D-S téměř nulové. Nárůst proudu na MOSFETu a výstupní indukčnosti odpovídá špičkovému proudu určenému odporem Q1, napětím na indukčnosti i vlastní hodnotou indukčnosti.

Během fáze sepnutí Q1 je energie vedena do výstupní indukčnosti a ve výstupním kondenzátoru dojde k akumulaci náboje. Odpovídající situace průtoku proudu Q1 je označena náhradním schématem se žlutou oblastí. Během této fáze je ztrátový výkon na Q1 definován především jeho vlastním odporem. Spínací ztráty jsou zde však prakticky zanedbatelné.

Následně dojde k vypnutí Q1, za čímž okamžitě následuje velmi krátké vedení proudu interní diodou, obvykle po dobu kratší než 10 ns. Tento stav představuje rovněž pouze zanedbatelný ztrátový výkon. V dalším kroku pak dojde k sepnutí Q2 a energie, která byla akumulovaná ve výstupní indukčnosti, je přenesena do výstupního kondenzátoru a připojené zátěže. I když pak indukční proud dosáhne své nuly, je synchronní MOSFET Q2 sepnut i nadále tak dlouho, aby naopak mohlo dojít k akumulování energie z výstupního kondenzátoru do indukčnosti. To je známý jev, při kterém obvodem teče proud opačným směrem. Uvedená situace je v náhradním schématu označena modrou barvou.

Jakmile regulátor rozhodne, že v indukčnosti je již dostatečné množství energie, vypne synchronní MOSFET a naopak sepne uzel VS směrem k výstupní svorce. Tím dojde k odpojení indukčnosti od výstupní svorky a vybití energie v podobě proudu v téměř bezeztrátovém spínači. Během této upínací fáze (která je velmi krátká) je proud dodáván pouze z výstupního kondenzátoru.

Jakmile upínací fáze skončí, dojde k rozepnutí výstupního spínače. V ten okamžik dochází k rezonanci energie akumulované ve výstupní indukčnosti s paralelní kombinací výstupních kapacit Q1 a Q2, čímž v bodě VS dojde k rezonanci napětí směrem k VIN. Tento stav však svou povahou snižuje účinek Millerovy kapacity Q1 a náboje ve výstupní kapacitě Q2. Díky tomu je možné sepnout Q1 v okamžiku, kdy je napětí v bodě VS rovné téměř hodnotě VIN, a tedy s minimální ztrátou. Tok proudu, včetně rezonančního přechodu, je uveden v ekvivalentním obvodu označeném zelenou barvou. Zde je však důležité poukázat také na skutečnost, že když je spínač na výstupu sepnutý, teče proud podle růžově označené části, a jakmile je spínač vypnutý, teče proud naopak podle červených šipek.

Obr. 6 Diagram časování ZVS regulátoru

Tato topologie řeší výše uvedené nedostatky hned v několika důležitých směrech:

- Dlouhá upínací fáze eliminuje nežádoucí vedení diodou, které před sepnutím tranzistoru MOSFET Q1 vyžaduje vysoký zotavovací proud.

- Ztráty při zapínání tranzistorů jsou zcela minimální.

- Budič Gate tranzistoru Q1 je ovlivněn parazitní indukčností Lshs. Účinek Millerovy kapacity na zapnutí je v obvodu ZVS zcela eliminován. To umožňuje použití budiče s menším výkonem, a tudíž i menší spotřebou energie. Jelikož tranzistor již nemusí spínat vysokou rychlostí, lze pozvolným náběhem výrazně redukovat produkovaný šum (EMI).

Srovnání pomocí simulace

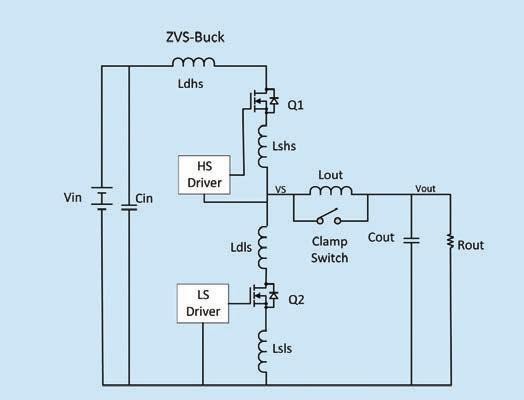

Obr. 7 Regulátor ZVS s parazitními indukčnostmi

Na obrázku 7 je zjednodušené schéma snižujícího ZVS regulátoru, včetně předchozích parazitních indukčností a jejich obdobných hodnot. I zde byla simulace provedena při vstupním napětí 36 V 12 V na výstupu při proudu 8 A a spínací frekvenci 1,3 MHz. Cílem simulace je porovnání ztrát v tranzistoru MOSFET Q1 se ztrátami z předchozího návrhu. Dále jsme zde použili 230 nH indukčnosti a tranzistory MOSFET se shodnou charakteristikou, stejně jako budičem, použitým v předchozí simulaci.

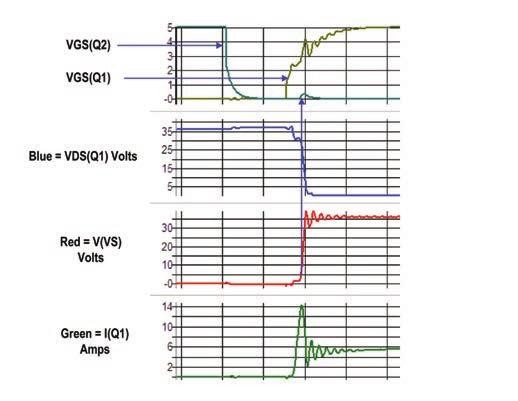

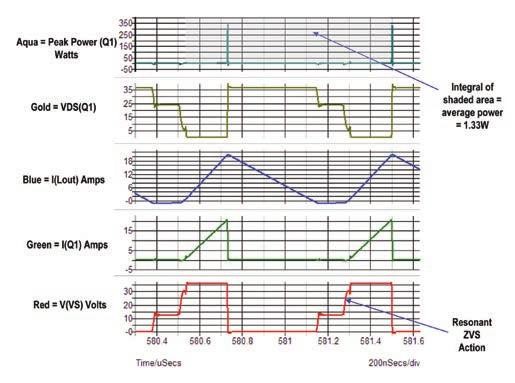

Obr. 8 Průběhy simulace snižujícího ZVS regulátoru s frekvencí 1,3 MHz a odpovídající křivky výkonu a proudu tranzistoru MOSFET Q1

Obrázek 8 ukazuje výsledky simulace snižujícího regulátoru ZVS topologie s frekvencí 1,3 MHz a jemu odpovídající křivky výkonu a proudu tranzistoru MOSFET Q1. Průměrný ztrátový výkon, včetně spínacích ztrát a ztrát ve vedení, vychází na 1,33 W u Q1, což je dokonce ještě méně než v případě konvenčního regulátoru provozovaného na poloviční spínací frekvenci a s větší indukčností. Úspory ztrátového výkonu Q1 při porovnání výsledků obou konstrukčních simulací při 1,3 MHz jsou pak ještě vyšší, tj. 1,37 W. Z výkonové křivky na obr. 8 je vidět, že ztráty při zapnutí jsou prakticky nulové a obvodem v ten okamžik neteče žádný velký proud. To je způsobeno tím, že v obvodu neexistuje žádná dioda ovlivňující obvod ještě před sepnutím Q1 ani se v obvodu neuplatňují žádné zotavovací proudy, včetně ztrát diody v Q2.

Obrázek rovněž ukazuje rezonanční přechod v ZVS vycházející z paralelní kombinace výstupních kapacit tranzistorů Q1 a Q2. Je dobře vidět, že sepnutí tranzistoru Q1 nenastane v okamžiku nulového napětí. Nejlepší účinnosti se u napájecích zdrojů dosahuje obvykle při spínání Q1 s nějakým zbytkovým napětím, čehož zde bylo dosaženo právě pomocí oběhu energie a upínací fáze. Obvod tedy využívá jednu z věcí vedoucích právě k minimalizaci ztrát spojených se spínáním versus úsporám energie ze spínání Q1. Rovněž budič tranzistorů může efektivně těžit z odstranění vlivu Millerovy kapacity, k čemuž došlo v důsledku působení ZVS topologie. Budič přitom nemusí „plnit“ celou kapacitu G-D přechodu Q1, takže ztráty v Q1 jsou tím pádem výrazně nižší. Kromě toho nemusí při zapnutí tranzistor bojovat proti parazitní indukčnosti Lshs, takže mu stačí menší náboj a nedochází ani ke ztrátě způsobené akumulací energie do Lshs.

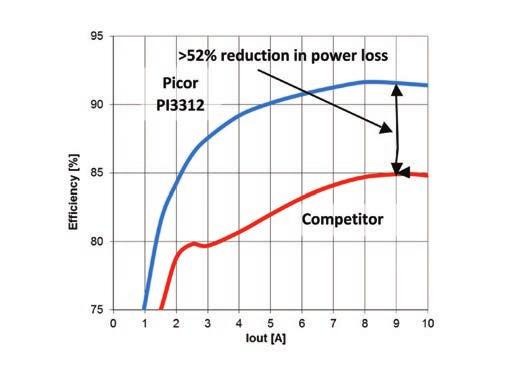

Obr. 9 Srovnání výkonu ZVS regulátoru s převodním poměrem 9,6:1, (24–2,5 V při 10 A) a konkurenčním řešení

Na obr. 9 je uveden rozdíl výkonu mezi konvenčním snižujícím regulátorem s přímým spínáním a topologií ZVS při Vin = 24 V a Vout = 2,5 V (9,6:1) při proudu 10 A. Rozdíl v účinnosti při plné zátěži je téměř 6,5 % (s výrazným rozdílem také při nízké zátěži), což při 9 A vede ke snížení ztrát o více než 52 %.

Další výhody

Díky integraci výkonného křemíkového regulátoru ZVS topologie Picor může rodina DC/DC převodníků řady PI33XX nabídnout široký rozsah vstupního napětí. Jedná se o moduly v provedení SIP s rozměry pouhých 10 × 14 mm, obsahující všechny obvody potřebné pro vytvoření napájecího systému pouze po přidání výstupní indukčnosti a několika keramických kondenzátorů. Vysoká spínací frekvence však umožňuje použití malých indukčností a celkové rozměry nepřevyšují hodnotu 25 × 21,5 mm. To je samozřejmě výrazně méně, než co nabízejí konkurenční integrovaná řešení, a přitom lze nabídnout výstupní výkon až 120 W s maximální účinností 98 %. Díky možnosti řízení již od 20 ns mohou obvody PI33XX pracovat od napětí 36 V na vstupu a 1 V na výstupu, při 10 A výstupního proudu a účinnosti lepší než 86 %. Maximální výstupní proud lze udržet v celém rozsahu výstupního napětí od 1 do 15 V.

Kombinací moderních křemíkových technologií a ZVS topologie bylo dosaženo hned několika zásadních výhod, mezi které patří mimo jiné široký rozsah vstupního napětí a vysoká účinnost. Vzhledem k tomu, že ZVS topologie zaručuje stabilní provoz s kontrolou funkce výstupního přenosu, čehož je zajištěno ziskem −1 a fázovým posunem o 90 stupňů, bylo možné použít širokopásmovou zpětnou vazbu podporující vysoké spínací frekvence. Obvody PI33XX pro svůj provoz nevyžadují použití žádné externí kompenzace (i když její použití se nevylučuje). Frekvence uzavřené regulační smyčky se pohybuje obvykle kolem 100 kHz s 55stupňovým fázovým rozpětím a 20dB rozpětím zisku. Široké možnosti regulace a malé rozměry výstupní indukčnosti umožňují použití širokého rozsahu spínací frekvence. Výsledkem jsou velmi rychlé reakce na přechodové stavy, s dobami zotavení pouhých 20 až 30 μs při použití jednoduchých keramických výstupních kondenzátorů a bez pomoci dalších velkých (akumulačních) kondenzátorů. Velmi přesná metoda řízení umožňuje chybovému zesilovači přesně odrážet výstupní požadavky a zároveň zajistit vysokou účinnost a stabilitu regulace. Autonomní provoz PI33XX vyžaduje pouze jediné připojení chybového zesilovače k monitorování zátěže. Pokud si uživatel přeje vzájemné řízení či synchronní provoz více regulátorů, lze samozřejmě obvody vzájemně propojit.

V případě obvodů PI33XX lze synchronizovat až šest paralelně zapojených jednotek. Uvnitř PI33XX je osazen téměř ideální synchronní usměrňovač, který podporuje pouze jednotkové měření a nanosekundové komutační intervaly mezi vypnutím Q1 a zapnutím synchronního MOSFETu. Tím jsou redukovány ztráty v tranzistoru MOSFET Q1 a jeho integrované diodě. Kromě vysoké účinnosti při velké zátěži jsou obvody PI33XX opatřeny monitorovacím systémem a režimem skládání pulsů, který vede k udržení vynikající účinnosti i při malé zátěži. Viz obr. 9.

Flexibilita

Architektura výkonných křemíkových regulátorů Picor využívá výstupních spínačů s téměř nulovým úbytkem napětí a může být aplikována i na ostatní topologie, jako jsou zvyšující regulátory či Buck-Boost obvody, pouze stačí přeskupit spínací prvky. Díky tomu lze zajistit vysokou účinnost konverze v prakticky libovolné kombinaci, a dokonce i při vyšším napájecím napětí, zatímco jsou v obvodu zajištěny nízké spínací ztráty, vysoká propustnost výkonu a v neposlední řadě také malé rozměry.

Závěr

Uvedený článek představil a podrobně popsal základní problémy, se kterými se lze setkat v případě konvenčních snižujících regulátorů na vysoké vstupní napětí a spínací frekvenci. Při provozu snižujícího regulátoru na vysoké frekvenci a velkém vstupním napětí je vždy žádoucí snížit celkovou velikost bloku napájecího systému tak, aby mohl být použit jako přímá náhrada za dvojfázové konverzní obvody a přitom nabídl ještě širší rozsah vstupního napětí a vysokou účinnost. V praxi bylo mnohokráte prokázáno, že pokud chceme v obvodu použít vyšší spínací frekvenci, je nejprve nutné redukovat zapínací ztráty výkonového tranzistoru MOSFET, nebo je v ideálním případě zcela eliminovat.

Topologie ZVS snižujících regulátorů byla prezentována jako prostředek vhodný k dosažení požadovaných rozměrů bez potřeby redukce výstupního výkonu. Nová řada produktů PI33XX využívá architekturu výkonných křemíkových budičů technologie Picor a obsahuje všechny funkce potřebné pro podporu širokého rozsahu vstupního napětí 8–36 V a řadu výstupních napětí, jako jsou 1 V, 2,5 V, 3,3 V, 5 V, 12 V a 15 V, při vysokém výstupním výkonu a celkové účinnosti. A nakonec jsme si vysvětlili, že stejná architektura výkonných křemíkových regulátorů může být použita i k řešení jiných napájecích topologií, jako jsou zvyšující nebo Buck- -Boost regulátory. Ve všech těchto případech lze použitím ZVS topologie dosáhnout vysokého výkonu a velmi dobré účinnosti.