Přirozeným popisem logických obvodů vycházejícím z historie je schéma zapojení. Takovýto popis neposkytuje příliš vysokou úroveň abstrakce a pro dnešní integrované obvody nebo rozsáhlé návrhy FPGA by byl takový funkční popis obrovský a velmi nepřehledný. Pro ověření funkce návrhu, tedy simulaci a verifikaci, jsou pak schémata naprosto nevhodná.

Především kvůli výše uvedeným důvodům se hledaly jiné způsoby popisu logických obvodů a jejich verifikace. Výsledkem je textový popis ve formě velmi podobné programovacím jazykům. Jedná se o jazyky HDL (Hardware Description Languages) zaměřené především na návrh číslicových obvodů, HVL (Hardware Verification Languages) zaměřené hlavně na simulaci a verifikaci a HDVL (Hardware Description and Verification Languages) určené jak pro funkční popis, tak i verifikaci.

Na tomto místě je třeba znovu zdůraznit, že přestože jazyky z rodin HDL, HVL a HDVL připomínají běžné programovací jazyky, jejich účel i principy jsou naprosto odlišné. Na rozdíl od programovacích jazyků nepopisují sekvenčně vykonávané činnosti, ale funkci distribuovaných logických obvodů.

V současnosti jsou nejpoužívanější jazyky z rodiny HDL Verilog a VHDL. Přestože se tyto jazyky liší syntaxí i sémantikou, oba poskytují obdobné prostředky k popisu logických obvodů. To, že jsou tyto HDL určeny převážně k popisu obvodů neznamená, že je není možné použít i pro simulaci a verifikaci. Pouze neposkytují tolik nástrojů pro formální verifikaci jako specializované verifikační jazyky.

Úroveň abstrakce

Jazyky Verilog i VHDL umožňují popis obvodů na různých úrovních abstrakce:

Behaviorální úroveň znamená popis chování obvodu na vysoké úrovni abstrakce. Tuto úroveň poskytují klasické HDL pouze částečně, ne všechny nástroje ji vždy podporují. Příkladem může být třeba nějaký komplexní výpočet v plovoucí řádové čárce zapsaný přirozeně ve formě matematické rovnice.

RTL úroveň je typická oblast nasazení klasických HDL. Jedná se o nižší úroveň abstrakce než behaviorální popis, kdy je funkce definována kombinací kombinačních a sekvenčních prvků. Popis na této úrovni je obvykle podporován všemi nástroji.

Strukturální úroveň popisuje vzájemné propojení jednotlivých funkčních modulů a je textovou obdobou blokových schémat.

Úroveň hradel popisuje obvod na nejnižší úrovni, kdy je funkce vyjádřena strukturou tvořenou jednotlivými logickými hradly. Tato úroveň odpovídá klasickému schématu zapojení.

Je obvyklé, že popis logického obvodu v HDL kombinuje několik úrovní abstrakce. Základem bývá RTL, kdy ale některé části jsou popsány na behaviorální úrovni. Hierarchie návrhu je realizována využitím strukturálního popisu, kdy jsou moduly na nižší hierarchické úrovni vkládány do vyšších úrovní.

Oblasti využití

Jak již bylo zmíněno výše, klasické HDL jsou určeny především k popisu funkce logických obvodů na různých úrovních abstrakce a částečně i k simulaci a verifikaci. To ovšem neznamená, že každá vlastnost jazyka může být vždy za každých podmínek využita. Obvykle se rozlišují podmnožiny jazyka použitelné pro syntézu, modelování a simulaci.

Syntetizovatelná podmnožina HDL je taková část jazyka, která může být použita pro popis logického obvodu a implementační nástroje ji dokáží přeložit do netlistu.

Podmnožina určená pro modelování obvodů nebo celých systémů může obsahovat buď vysokoúrovňové vlastnosti jazyka, které nepodporují implementační nástroje, nebo základní vlastnosti, které nejsou z principu implementovatelné, jako jsou například definovaná časová zpoždění. Tato podmnožina může být využita pro modelování funkce obvodu nebo systému s využitím číslicového simulátoru, ale už ne pro jeho implementaci v hradlovém poli nebo třeba ASIC.

Do simulační podmnožiny HDL patří vlastnosti jazyka určené k řízení simulace a verifikaci funkce simulovaného obvodu. Tato část jazyka opět není podporována implementačními nástroji, ale pouze simulátory.

Verilog

V osmdesátých letech firma Gateway Design Automation uvedla na trh číslicový simulátor Verilog-XL a s ním i jazyk pro popis číslicových obvodů Verilog HDL. V roce 1989 pohltila Gateway firma Cadence Design Systems i s autorskými právy na jazyk a simulátor. V roce 1990 dala firma Cadence jazyk (ale ne simulátor) k dispozici jako public domain se záměrem, že se z něho stane standard. Verilog HDL je od té doby udržován neziskovou organizací Open Verilog International (dnes Accellera) a prošel standardizační procedurou IEEE (Institute of Electrical and Electronics Engineers). Verilog byl standardizován v roce 1995 jako IEEE Std. 1364-1995. Tato verze jazyka se označuje jako Verilog-95. Od té doby prošel Verilog mnoha rozšířeními, po nichž byl jazyk standardizován jako IEEE Std. 1364-2001 (označovaný jako Verilog-2001) a IEEE Std. 1364-2005 (Verilog-2005).

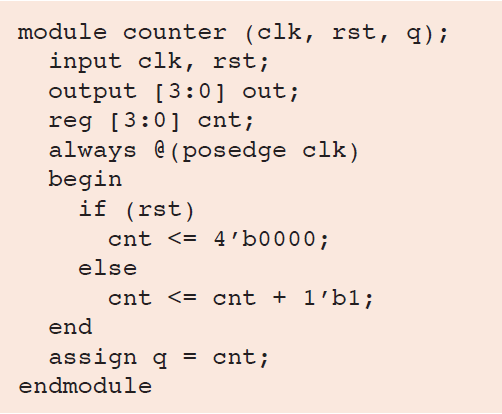

Samotný popis jazyka přesahuje rámec této publikace. Zájemce o výuku najde odkazy na literaturu v závěrečné části. Pro bližší představu o syntaxi může posloužit následující příklad syntetizovatelného popisu jednoduchého čtyřbitového synchronního čítače na úrovni RTL:

Tento kód popisuje funkční blok pojmenovaný counter, který má dva vstupy clk a rst a jeden čtyřbitový výstup q. Blok kódu uvozený always je aktivovaný při každé vzestupné hraně hodinového signálu clk. Pokud je přitom aktivní signál rst, interní registr čítače cnt se vynuluje. Pokud je reset neaktivní, dojde k inkrementaci hodnoty registru o jedničku. Výraz za assign neustále přiřazuje hodnotu interního registru cnt na výstup q.

VHDL

Název jazyka VHDL je zkratka VHSIC Hardware Description Language, přičemž VHSIC je opět další zkratka pro Very High Speed Integrated Circuit. Vývoj VHDL začal roku 1981 na popud amerického ministerstva obrany. Důvodem byla narůstající nereprodukovatelnost elektronických systémů z důvodu nedostatečné dokumentace nebo naopak neúnosně dlouhá doba strávená tvorbou dokumentace a především to, že jednotlivé části systému byly vyvíjeny a simulovány mnoha různými nekompatibilními nástroji. Požadavkem bylo vyvinout jazyk s širokou popisnou schopností, který bude interpretován stejně jakýmkoli simulátorem a bude nezávislý na technologii a návrhové metodice.

V letech 1983 až 1985 pracovalo na specifikaci mnoho firem, jako například Intermetrics, IBM, Texas Instruments. Roku 1986 byla práva převedena na organizaci IEEE, která roku 1987 publikovala první verzi jazyka IEEE Std. 1076-1987, označovanou jako VHDL-87. K jazyku VHDL se úzce váže standard IEEE Std. 1164, který definuje další logické datové typy, které kromě dvou základních logických úrovní 0 a 1 mohou vyjádřit další stavy, jako například vysokou impedanci, otevřený výstup, kolizi několika budičů a podobně.

V roce 1993 byla vydána revidovaná verze jazyka jako IEEE Std. 1076-1993, označovaná VHDL-93. Poté bylo vydáno několik doplněných a rozšířených verzí standardu (2000 a 2002), bylo doplněno několik dalších rozšíření standardu 1076 pro další datové typy, jako jsou celá a reálná čísla apod. Důležitým krokem bylo delegování organizace Accellera správou standardu VHDL. Výsledkem pak byla publikace standardu IEEE Std. 1076-2008 (VHDL-2008), který přinesl mnoho významných rozšíření jazyka a integroval dodatečné standardy z rodiny 1076.

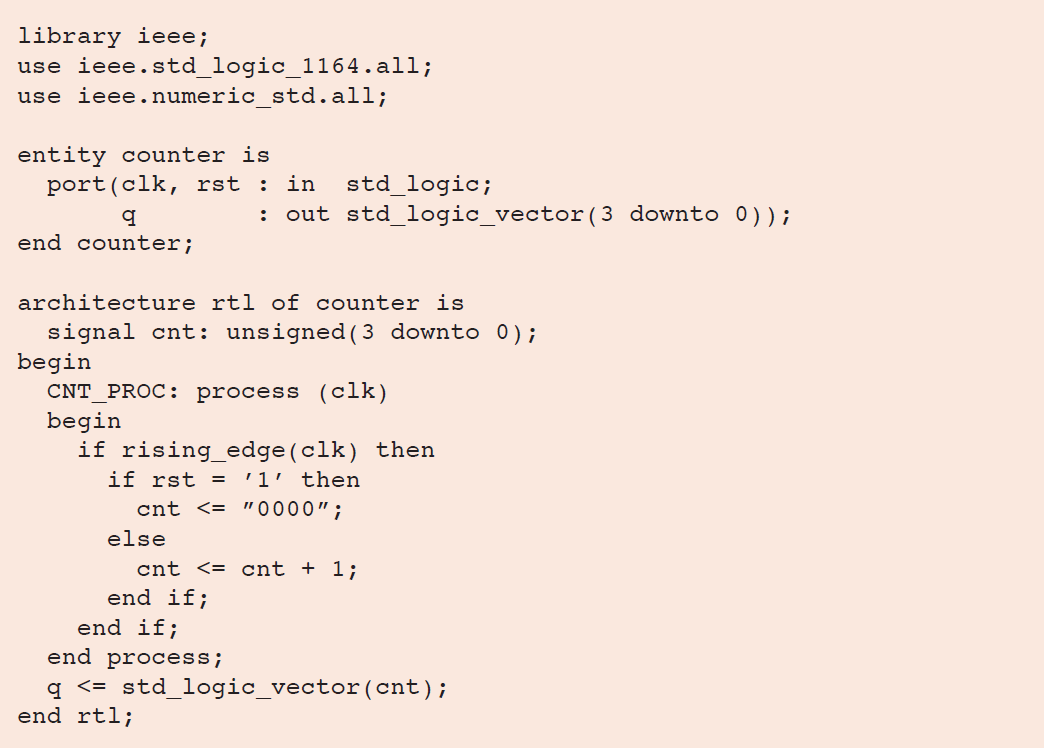

Popis jazyka přesahuje rámec této publikace. Odkazy na podrobnou literaturu budou uvedeny v závěrečné části. Následující ukázka představuje syntetizovatelný popis čtyřbitového synchronního čítače:

Tento kód implementuje stejnou funkci jako předchozí kód ve Verilogu. Porovnáním těchto dvou příkladů jsou zjevné dva největší rozdíly mezi VHDL a Verilogem:

Vysokoúrovňové jazyky

Kromě klasických HDL existují i další jazyky určené k popisu logických obvodů, které ale popisují obvody na vyšší úrovni abstrakce. Často se jedná o jazyky založené na některých klasických programovacích jazycích, jako je třeba C nebo Python. Vývojová prostředí pak přinášejí kromě vlastního kompilátoru i sady knihoven funkcí implementující některé operace.

Příkladem vysokoúrovňových jazyků pro popis číslicových obvodů vycházejících z jazyka C je HLS od firmy Xilinx, Catapult C od Mentor Graphics nebo třeba Handel-C původně od firmy Celoxica. Velmi slušně udržovaný a rozvíjený open- source projekt je MyHDL, který využívá podmnožinu jazyka Python.

S růstem velikosti a složitosti integrovaných obvodů a programovatelné logiky přestávalo stačit ověření funkce logických obvodů pomocí jednoduchých simulací. Začaly vznikat různé metody formální verifikace a společně s nimi i jazyky umožňující tyto metody implementovat. Jedná se o jazyky jako Vera, e, částečně PSL, ale také třeba C nebo C++ a z něj vycházející SystemC. Tyto jazyky jsou často kombinovány s klasickými HDL. Jak Verilog, tak i VHDL například obsahují podporu pro PSL (Property Specification Language) a umožňují tak psát samotestovací kód přímo v popisu logického obvodu. Vlastní verifikační prostředí pak bývá realizováno v některém verifikačním jazyce, který umožňuje formální verifikaci obvodu s využitím metod založených na tzv. „constrained random“ technikách řízených pomocí „functional coverage“ a využívajících „assertions“. Bohužel pro tyto výrazy neexistují v kontextu funkční verifikace české ekvivalenty.

Jazyky založené na C nebo C++, jako je třeba SystemC, poskytují další možnosti využití. Kromě vlastní (formální) verifikace umožňují například modelovat celé systémy zahrnující kromě logických obvodů i procesory a funkce realizované softwarově.

SystemVerilog

Samostatnou kapitolou kombinované jazyky určené jak pro popis logických obvodů a komplexních systémů, tak i pro verifikace. Hlavním představitelem těchto HDVL je SystemVerilog. SystemVerilog je velmi výrazné rozšíření jazyka Verilog-2005. Rozšíření se týkají především podpory modelování komplexních systémů a formální verifikace. Je zajímavé, že standardy jazyků Verilog a SystemVerilog byly v roce 2009 sloučeny do jednoho společného standardu IEEE Std. 1800- 2009. Momentálně aktuální verze jazyka je standardizována IEEE Std. 1800-2012 (SystemVerilog-2012).

Samotný jazyk SystemVerilog je možné rozdělit na dvě podmnožiny:

Část jazyka určená pro RTL vychází z Verilogu ve verzi 2005. Navíc přináší mnoho nových datových typů, nové typy procedurálních bloků, rozšířené operátory, nové výrazy a mnoho dalších rozšíření.

Verifikační podmnožina jazyka je založená na principech objektově orientovaného programování. SystemVerilog přináší především objektové třídy, generování rozsahem omezených náhodných čísel, vektorů a řad (constrained random), vlastní způsob definice assertions a podporu pro functional coverage.

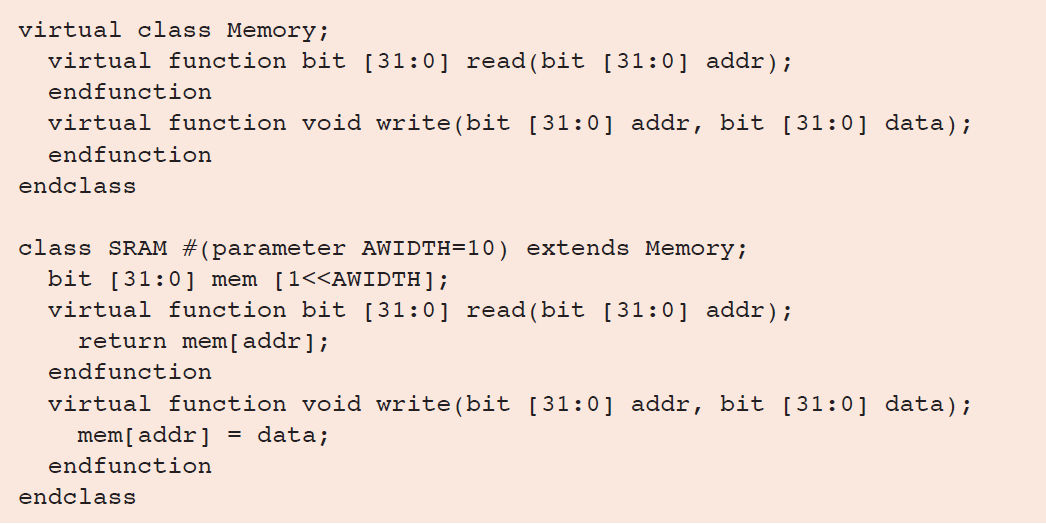

Kód čtyřbitového synchronního čítače v jazyce SystemVerilog by byl shodný s kódem ve Verilogu uvedeným výše. Lepší ilustrace jazyka proto bude jednoduchý příklad objektově orientovaného kódu. Následující příklad je převzat z Wikipedie (heslo SystemVerilog):

Tento kód deklaruje třídu Memory, která má dvě virtuální metody read a write. Z třídy Memory je odvozena nová třída SRAM, která pro paměť typu RAM definuje pole 2AWIDTH dvaatřicetibitových vektorů jako paměťovou matici a definuje funkci virtuálních metod read a write. Metoda read vrací slovo z adresy addr, metoda write zapisuje slovo data na adresu addr. Třída SRAM tedy reprezentuje statickou paměť typu RAM s okamžitou odezvou.