Po padesáti letech od první, komerční programovatelné logické součástky jejich současná výbava umožňuje vývojářům proniknout do celé řady odvětví.

Hradlová pole FPGA (field-programmable gate array) a další programovatelné logické obvody jsou nyní ještě výkonnější a také univerzálnější. Zahrnují přitom funkce, které bývaly tradičně řešené s využitím CPU, GPU a DSP. Až by jeden řekl, že půjde o jakýsi polovodičový protějšek švýcarského nože pro armádu.

Prvky FPGA mohou vykonávat složitější funkce než jejich nejbližší příbuzný, obvod CPLD (complex programmable logic device). Jsou také zcela novým odrazovým můstkem, se kterým dokážou vývojáři zapracovat své vlastní funkce a nemusí přitom nutně vycházet z předem dané nabídky výrobce. Hradlová pole FPGA bývají neuvěřitelně všestranná, zajišťují výpočty, zpracování signálu, vysokorychlostní komunikaci a mnoho dalšího, to vše bez potřeby vnějších periférií. Na rozdíl od standardních struktur ASIC (application-specific integrated circuit), které někdy i nahrazují, lze pole FPGA navíc přeprogramovat přímo v místě nasazení a nezřídka bez nutnosti změny hardwaru.

Definice řady spojení a také funkcí logických buněk nebyla u polí FPGA nikdy jednodušší. Ve snaze odlehčit vývojářům vytvořili jak výrobci FPGA, tak i dodavatelé návrhového softwaru speciální nástroje. Nechybí zde ani předem navržené a ověřené funkční bloky, se kterými je programování polí FPGA zase o něco snazší.

Koncem šedesátých let se v celosvětovém měřítku stalo několik významných událostí. První let Concordu, přistání Apolla 11 na Měsíci, inaugurace prezidenta Nixona. Výskyt programovatelného hradlového pole XC157 v „The Integrated Circuit Data Book“ proto mohl ve stínu výše uvedeného zůstat bez povšimnutí. Jednalo se však o mimořádný okamžik. Zařazení součástky s 12 hradly a 30 I/O piny pro vstupy a výstupy zde představovalo klíčový milník ve vývoji programovatelných logických obvodů. Nyní se jednalo o komerční záležitost.

Další vývoj pokračoval rychlým tempem. Koncem osmdesátých let zapojil program US Naval Surface Warfare Department účastníky z průmyslové sféry do vytvoření počítače s 600 000 programovatelnými hradly. Netrvalo dlouho a zakladatelé Xilinx, Ross Freeman a Bernard Vonderschmitt, představili první komerční pole FPGA XC2064. Součástka byla maticí konfigurovatelných logických bloků CLB 8×8, což zde představovalo 64 bloků CLB společně s párem třívstupových tabulek LUT (look-up table).

Dalších více než třicet let a věci jsou opět jinak. Moderní hradlová pole FPGA se mohou pochlubit svými vlastními jádry procesoru (třeba jako ARM Cortex), 50 milióny logických prvků, obrovskou velikostí vysokorychlostní paměti, vlastními analogově-číslicovými převodníky (ADC) a 128bitovým šifrováním. Během zpracování číslicového signálu dokážou provádět bilion operací s plovoucí čárkou za vteřinu (teraflops), zatímco nabízí malou prodlevu a celkovou propustnost napříč všemi sériovými kanály transceiveru, takřka až do 3 Tb/s. To vše je k dispozici v rámci jediné součástky vyžadující malé množství energie, což ze současných polí FPGA činí mimořádně všestranné systémy SoC (systems-on-chip). Komunikační systém, který mohl kdysi pro zajištění počátečních funkcí receiveru např. vyžadovat několik obvodů ASIC (application-specific integrated circuit) si tak nyní vystačí s jediným hradlovým polem FPGA.

Další zastávka na pozoruhodné cestě polí FPGA se bude týkat výpočetní techniky s možností rekonfigurace. V takovém případě pak FPGA ve spojení se softwarem nabízí plný rozsah funkcí počítače s přispěním všestranně použitelného procesoru pro řídicí účely. Myšlenka, o které se poprvé hovořilo již v šedesátých letech, byla názorně předvedena v roce 1991 u CHS2x4 od Algotronix. Zmíněná deska využila pole FPGA CAL1024 od Algotronix s 1024 programovatelnými buňkami (1,5μm technologie double metal CMOS). Jednalo se o první FPGA, které svou řídicí paměť vybavilo nahodilým přístupem, nabídlo sdílení I/O signálů a vývojáři zde mohli vytvářet pole součástek. Tento kousek byl tak průlomový, že Xilinx o pár let později technologii IP od Algotronixu zakoupil.

Výpočetní technika s možností rekonfigurace na základě polí FPGA byla u specializovaných špičkových systémů příjemným překvapením. Vezměme si třeba Cost-Optimized Parallel COde Breaker (COPACOBANA), automat navržený pro práci se šifrovacími algoritmy, jako je Data Encryption Standard (DES), stejně jako pro další paralelní výpočetní úlohy.

COPACOBANA ale není univerzálním počítačem. Jeho taktovací rychlosti jsou totiž výrazně nižší než ty, které můžete získat od zařízení stavějícího na CPU. A omezení zde máme rovněž na straně rychlosti komunikace nebo šířky pásma. V případě typu úloh, pro které byl navržen, je však nesmírně výkonný, a protože využívá jedině standardních součástek a polí FPGA, těží též i z výrazně nižší ceny, než je tomu u šifrovacích počítačů vystavěných na CPU.

COPACOBANA s ovládáním prostřednictvím standardních Windows nebo Linux PC má v závislosti na konkrétním řešení zhruba 120 polí FPGA a provádí 48 miliard dešifrovacích operací (DES) za vteřinu. K tomu vyžaduje pouze 600 wattů.

Schopnost systému lze dokumentovat na vlastnostech hardwaru pro kryptoanalýzu při testování tajného klíče na workshopu Cryptographic Hardware and Embedded Systems 2006, kde byl klíč objeven do 21,5 hodiny (prohledáno méně než 5 % prostoru a s uvážením 43 miliard klíčů každou vteřinu).

Mezi nejnáročnější výpočetní aplikace, které můžeme najít, zařadíme kupříkladu práci s tajnými informacemi ukrytými v signálech, boje vedené s využitím elektroniky a také oblast radarů. Nelze se proto divit převažujícímu názoru, že takové náročné úkoly zvládnou jen superpočítače. Nicméně své zde mají co říci též i hradlová pole FPGA se svou nízkou spotřebou, výkonným paralelním zpracováním či I/O a také aritmetickými předpoklady pro práci s plovoucí čárkou.

Jako příklad rodiny hradlových polí FPGA vhodných pro takové náročné aplikace si uveďme Stratix 10. Více než čtyři milióny logických prvků jsou zde vyrobeny s využitím 14nm tri-gate procesu od Intelu. Systém zahrnuje 64bitové čtyřjádrové procesory ARM Cortex-A53, které nabízí čtyřikrát větší propustnost dat než jejich předchůdci. A čtyřnásobná bude rovněž šířka pásma sériového transceiveru. Každá jednotka kromě toho vychází z 28 Gb/s, mezi čipy nebo ve vztahu čip–modul uvažuje 56 Gb/s, pro šířku pásma sériové paměti počítá s více než 2,5 Tb/s, šířka pásma u rozhraní paralelní paměti činí 1,3 Tb/s a nechybí zde ani podpora paměti DDR4 s 3 200 Mb/s. Požadavek na operace s plovoucí čárkou je dále podporován výkonem DSP 10 teraflops (single-precision).

Výkonové nároky zmíněných součástek jsou také výrazně nižší, než je tomu v případě předchozí generace špičkových FPGA (100 GFLOPS/W, single-precision floating-point, asi o 70 %). Vývojáři pracující s rodinou Stratix 10 navíc získávají přístup k rozsáhlé nabídce návrhových a vývojových nástrojů od Altera.

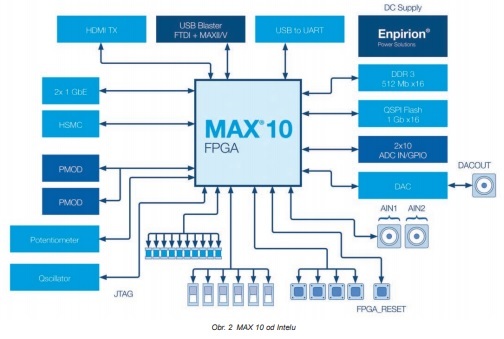

Jasně, vaše aplikace asi nepotřebuje takovéto špičkové možnosti. Stále však může vyžadovat o něco víc, než dokážou nabídnout běžná hradlová pole FPGA. V takovém případě zvažte model střední třídy typu polí FPGA MAX 10. Zmíněné součástky zahrnují podporu embedded soft procesoru, kontroléry paměti, DSP, analogové bloky s 12bitovými A/D převodníky, teplotní čidlo, smyčky fázového závěsu PLL a také komplexní hodiny s malou odchylkou. Kromě toho je zde k dispozici až 736 kB paměti Flash (dual-configuration), což znamená, že můžete na jednom čipu uložit dva obrazy a dynamicky mezi nimi přepínat. Navíc jsou připravené k okamžitému použití, takže je lze upotřebit při řízení zapínání nebo inicializaci systémových součástí. Hradlová pole FPGA MAX 10 nabídnou mezi 2 000 až 50 000 logických prvků, 18 analogových vstupních kanálů, až 500 uživatelských I/O pinů a také 128bitové AES (advanced encryption standard).

U mnoha polí FPGA využívaných v naprosto běžných aplikacích se také jedná o výkonné součástky. Rodina FPGA MachXO3 od Lattice Semiconductor je např. mimořádně kompaktním a cenově efektivním řešením ve snaze přemostit nově vznikající rozhraní vzájemné propojitelnosti jak se sériovými, tak i paralelními I/O. Bondované vodiče jsou díky technologii zapouzdření od Lattice již věcí minulosti, takže je možné jít s cenou dolů a zvyšovat i hustotu vstupů a výstupů. Různá pole FPGA mívají v rámci rodiny MachXO3 mezi 640 a 6 900 LUT. Využijeme je při řízení v průmyslu, v automobilovém sektoru, spotřební elektronice, při bezdrátové komunikaci, ve výpočetní technice a také úložištích. A podobně jako v dalších případech, které jsme již zmiňovali, jsou k dispozici rovněž nástroje, návrhy a jiné podpůrné materiály určené pro vývojáře, kteří s takovými poli pracují.

A ještě něco dalšího. Terasic nabízí svou platformu Cyclone V GX Starter Kit, se kterou pomůže všem těm, kdo navrhují hardware. Používá přitom pole FPGA Cyclone V GX. Deska pamatuje na header pro Arduino, vysokorychlostní transceivery, USB blaster a také možnosti pro A/V.

Když už tady „kážeme“ o polích FPGA, nesmíme zapomenout, že nejsou jedinou formou programovatelných logických obvodů, které můžete využít. Podmanivou šíři funkcí v rámci jediné součástky nabídnou i jiní, třeba jako programovatelná PSoC (programmable system on a chip) od Cypress Semiconductor. PSoC od Cypress jsou zde unikátní, protože půjde o jediný programovatelný vestavný SoC s mikrokontrolérem, pamětí, programovatelnou logikou stavějící na PLD a také špičkovými analogovými bloky. To vše na čipu a stále s předpoklady pro velmi nízkou spotřebu energie. Rodina PSoC 5 na špici rozsahu využívá řešení pro smíšené signály s poslední generací ARM Cortex-M. CY8C56LP jako součást řady PSoC 5 vám nabízí konfigurovatelné bloky s číslicovými nebo též analogovými obvody a také prvky pro vzájemnou propojitelnost, to vše vystavěné okolo subsystému s CPU. Spojení CPU s I/O, směrováním a jak analogovými, tak i číslicovými subsystémy zde představuje lákavou nabídku pro spotřební, medicínské a také průmyslové aplikace. Digitální subsystém využívá svých možností vzájemného propojení k efektivnímu provázání číslicového signálu přicházejícího z periférií na jakýkoli pin. Funkční flexibilitu pak zajišťují bloky UDB (universal data block). Programování a konfigurace této součástky neznamená v zásadě nic složitého. Periférie PSoC Creator library jsou všechny mapovány do pole UDB. Zahrnuje to funkce časovače, čítače, AND, OR, PRS, CRC, UART, SPI, LIN a také PWM. Každý blok UDB pak obsahuje programovatelné logické funkce a dále i malý stavový automat a umožňuje tak pracovat s celou řadou periférií. Vývojáři zde mohou využít i konfigurovatelných digitálních bloků pokrývajících možnosti propojení přes USB, CAN 2.0 a I²C slave/master.

Na samotný konec ještě zmíníme příklad, kterým demonstrujeme, jak univerzální a efektivní jen mohou být moderní programovatelné logické obvody. Úplný subsystém pro zachytávání signálu a jeho zpracování si nyní můžete vytvořit jen se třemi kartami formátu OpenVPX. Mezi klíčové součásti zde patří pár špičkových polí FPGA společně s nezbytnými ADC a DAC pro převod dat a dále pak i čtyřjádrový procesor Intel Core i7, související paměť, I/O a transceivery SERDES. Pole FPGA, stejně jako šířka pásma a vzorkovací kapacita podpůrných obvodů pro zpracování signálu jsou tak výkonné, že výše zmíněná sestava o třech kartách pak může zachytávat signály přímo ze vzduchu, a to s rychlostmi až do 6 GHz. Abychom něco takového mohli ještě před několika málo lety realizovat, bylo by zapotřebí řešení, které na desce plošného spoje spotřebuje takřka řádově více místa. S tím, jak programovatelné logické součástky těží z ještě větší popularity, roste i tempo současných inovací. Pravda, zmíněná technologie se mohla od šedesátých let minulého století vyvíjet, nicméně dnes, o více než padesát let později, s ní dokážeme skutečně pozoruhodné „kousky“.