Tranzistory MOSFET na bázi karbidu křemíku, tedy SiC? Určitě ano. Jen si dobře pohlídejte způsob, jakým je hodláte řídit. Abyste kromě výkonového tranzistoru nemuseli ještě spínat i ruce.

Pojďme rovnou k věci. Součástková základna od společnosti STMicroelectronics se nedávno rozrostla [1] o jednokanálové budiče hradla s označením STGAP2SiCSN právě pro účely ovládání výše zmiňovaných MOSFETů. Výrobce je nabízí v pouzdrech typu SO-8 „narrow-body“, se kterými hodlá zajistit nejen robustní provedení, ale také nezbytné, přesné řízení s pulzně-šířkovou modulací PWM. Technologie SiC má při zvyšování účinnosti konverze napájení rozhodně co říci. Novinky od ST pak vše jen podtrhnou, zvláště když u energeticky „uvědomělých“ zdrojů, pohonů a také systémů řízení zjednoduší celý návrh, ušetří nějaké to místo a ještě i pozvednou spolehlivost. Máme tím na mysli třeba nabíjení elektrovozidel, spínané zdroje napájení, korekci účiníku PFC, DC/DC měniče, zálohované systémy UPS, solární zdroje, řízení motorů, ventilátory, tovární automatizaci, domácí spotřebiče, indukční ohřevy a mnoho dalších zapojení skloňujících výkony.

Obvody STGAP2SiCSN využijí mezi kanálem pro buzení hradla a nízkonapěťovým řízením služeb galvanického oddělení, pro které výrobce uvažuje provozní napětí mezi jednotlivými zeměmi na úrovni až 1 700 V. K tomu si připočtěme průchozí zpoždění pod 75 ns nahrávající přesnosti systému s PWM a také spolehlivé spínání z titulu odolnosti CMTI (common-mode transient immunity) ±100 V/ns. Vestavěná ochrana pak zahrnuje podpěťový zámek UVLO s prahovou úrovní nastavenou tak, abychom výkonovým spínačům na bázi SiC zamezili pracovat s malou účinností, příp. za nebezpečných podmínek. K tomu se dále přidává i teplotní pojistka stahující oba výstupy budiče při zaznamenání nadměrné teploty.

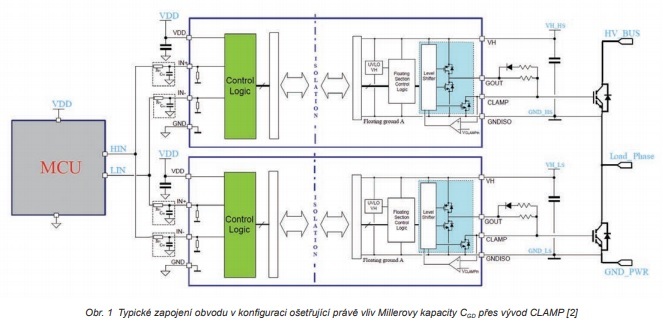

V množném čísle zde nehovoříme jenom tak, protože firma STMicroelectronics u svých obvodů STGAP2SiCSN přichází se dvěma různými konfiguracemi. Vývojáři mají proto možnost pracovat na základě samostatných výstupů a nezávisle si zde s přispěním vnějších rezistorů optimalizovat časování nebo si vše ošetří s jediným výstupem, který již díky uspořenému vývodu dokáže aktivně dále pracovat s Millerovou kapacitou. To pak v praxi znamená, že máme hradlo vnějšího spínacího tranzistoru během vypnutí sledováno prostřednictvím vývodu CLAMP. Jeho pomocný spínač lze tedy v návaznosti na vzniklé napěťové poměry aktivovat a vytvořit přitom trasu s nízkou impedancí vedoucí mezi příslušným hradlem a pinem GNDISO. Pomůžeme tím stabilitě bez nepřiměřených oscilací výkonového prvku – viz také zapojení dle obr. 1.

Logické vstupy obvodu jsou kompatibilní s logikou TTL a CMOS již od 3,3 V, což dále zjednoduší spojení s host mikrokontrolérem či signálovým procesorem. Při uvážení napětí na hradle o velikosti až 26 V pak budiče slouží jako zdroj či nora s průtoky až do 4 A. Návrh pomáhá zjednodušit vlastní bootstrap dioda, zatímco se lze dopracovat i k funkci standby spouštěné dvěma jedničkami na vstupech po předem stanovenou dobu.

[1] Tisková zpráva, https://newsroom.st.com/media-center/pressitem.html/n4399.html

[2] Obvody STGAP2SiCSN, https://www.st.com/en/powermanagement/stgap2sicsn.html